為了實現像是由人工智慧(AI)驅動、具備情境感知與半自動能力的數位雙生等未來科技應用,現代的運算系統需要超越摩爾定律,在性能方面達到數倍升級。

要讓每總體擁有成本(TCO)的晶片性能躍升,系統級設計、軟硬體(電晶體)協同設計優化、同時探索先進算力,以及多元化的專業團隊與能力,全都至關重要。

在數分鐘內完成血液滴樣的基因體分析或蛋白標記,同時降低檢測費用。提供高動態無損的擴增實境(AR)與虛擬實境(VR)環境,實現流暢互動。信賴半自動化且具備情境感知能力的AI私人助理,對我們個人的數位雙生進行監控。展望未來,透過整合高效能運算與AI系統,人類似乎獲得了改善生活的無數可能。然而,這些可能至少會受限於現有的運算系統,包含其運算能力與節節升高的成本。這項挑戰不容輕視,因為這些新興應用全都需要晶片性能與能源效率達到數倍升級,同時抑制成本增加。

很可惜,運用目前的高效能或AI硬體,我們很難以傳統的微縮技術來建構這樣功能強大的系統。我們不能為了達到目標而一味增加處理核心或記憶體,這會導致元件尺寸、能耗與成本呈現不合理地爆炸性增長。

那我們為何不一如既往,延續晶片微縮規模呢? 有哪些主要困難? 此外,我們能採取什麼策略來提升運算能力與能源效率,同時顧及整體成本?

系統微縮的門檻調高

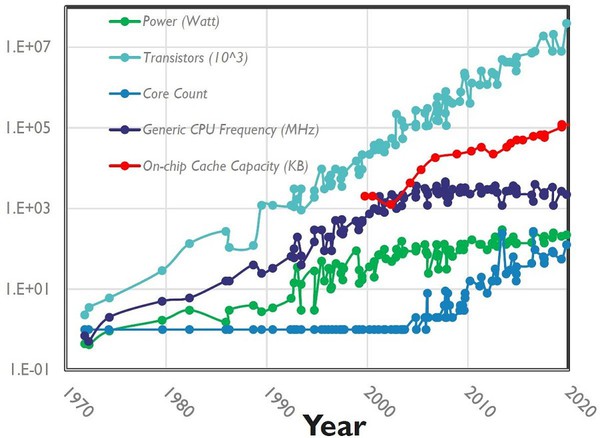

50多年來,摩爾定律與Dennard縮放定律一直是晶片性能代代升級與維持穩定成本的基礎;前者意味著在相同的晶片面積與成本下,電晶體數量大約每兩年翻漲一倍,後者則是在電晶體微縮時維持功率密度不變。但在過去10幾年間,受到這些定律啟發的尺寸微縮策略顯然不再能滿足未來運算系統的微縮目標。其中包含好幾項因素,我們稱作微縮障壁(scaling walls),可分為尺寸障壁、記憶體/頻寬障壁、功耗/熱障壁以及成本障壁。

雖然相同面積下的電晶體數量還是維持每兩年翻一倍,但業界在採用複雜的系統設計時面臨了超乎常理的高昂成本,以及處理速度與功耗問題。舉例來說,在傳統的馮紐曼電腦架構下,晶載快取記憶體的微縮速度已經趕不上邏輯元件,而且傳輸速度也越來越難達到處理器所需的水準。除了記憶體/頻寬障壁,漏電現象也破壞了Dennard縮放定律的發展,導致散熱與頻率停滯問題,與此同時,先進製程的成本也在飆漲。

從架構著手,在系統單晶片導入複雜的記憶體階層、多核處理器與專用加速器(xPU)成為克服這些微縮障壁的解決辦法。儘管目前多核設計當道,處理器隨著微縮技術演進而步入先進製程,但在改良性能、功耗、尺寸與成本(PPAC)方面卻開始面臨發展飽和。

| 圖一 : 採用傳統馮紐曼架構的處理器性能演變,包含電晶體數量、核心數量、功耗、CPU時脈、快取記憶體速度。 |

|

萬物齊漲 著手解決「創新者困境」

加上隨之而來的龐大成本障壁,可見「算更快、省更多」的快樂微縮時代已經結束。過去,半導體產業在考量成本時較為狹隘。據分析,每採用新一代製程技術,每平方毫米(mm2)的相對成本都會減少,如同摩爾定律的預測。然而,半導體製程與系統設計日趨複雜,因此整體成本不再下降。除了先進製程的封裝成本上揚,系統運作期間的散熱與功耗、設備維護等,都在逐步拉抬總體擁有成本。因此,每總體擁有成本的性能正在下滑,相同尺寸下的系統成本也在逐漸增加。

這些因素造成了所謂的「創新者困境(the Innovator's Dilemma)」,這也是所有企業在運營既有業務的同時,投入破壞性創新開發與投資時都會面臨的挑戰,這些業務透過導入能維持市場價值的永續科技,進而將其推向市場。考量每總體擁有成本的性能升級幅度,當前的挑戰是持續推動技術快速升級,比照我們見證的AI與高效能運算發展。實現數倍的性能升級是我們研發的主要動力。

我們確信,要取得運算效能的空前進展,唯一方法就是動用整體晶片系統的創新資源,涵蓋演算法到核心元件。而且這些創新應該從最一開始就進行協同設計才能確保整體成本最佳化。這些原則是比利時微電子研究中心(imec)運算系統架構(Compute System Architecture)研究項目的指引。

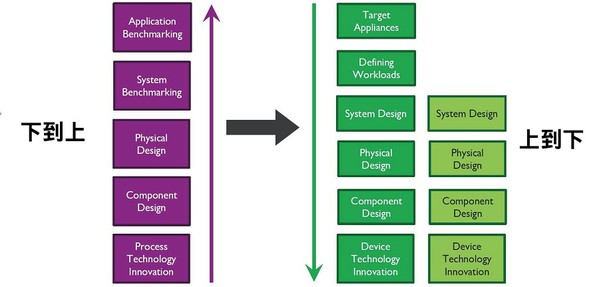

顛覆傳統 由上而下的系統設計

系統設計的思維是由上而下建立整體系統架構。傳統上,摩爾定律的微縮進程驅動了不少技術發展:有了全新的電晶體架構就能開發新興元件,接著就能堆疊元件,設計更高效的電路、記憶體和處理器。然而,這種由下而上的設計方法限制了整體晶片系統進行協同設計的可能性。

| 圖二 : 比較「由下而上」的傳統方法與「由上而下」的設計方法。 |

|

以系統架構為考量的設計方法認為應用需求勢必會驅動解決方案。我們要讓目標裝置驅動元件與系統架構的創新,而不是選用現有硬體來解決問題。我們正在發展一種設計思維、框架與研究方法,使得整個元件都能持續進行由應用驅動裝置的協同設計。

具備時下影響力的應用將會推動系統開發,預測未來幾年的產業與社會需求。

從架構到技術的優化循環

開發未來的運算系統架構,先要了解目標應用的需求,以及背後運作所需的關鍵規格與演算法。

假設我們以全基因體快篩為目標應用,那麼適用的規格可能是要用來分類基因缺陷。隨後,我們針對目標應用來預測未來需要採用的軟體、運算系統與關鍵元件模組,把整體系統納入考量:我們界定不同抽象層所需的創新,包含演算法、架構模型化、性能分析與實際執行。

接著,架構模型化與分析提供每總體擁有成本的預期系統性能,並提出設計建議以實現目標性能。在系統層級取得的性能優勢將會源於不同抽象層之間的各種交互優化。這些優化相輔相成,理想的話還能帶來數倍的性能升級。這就是根本性重複的協同設計循環。

這套模型以總體擁有成本的性能為指標,該指標帶領我們進入後續流程。這套流程可能包含重構演算法、評估不同的系統設計,甚至可能進行原型設計,藉此開發具備規模化、可靠度與能源效率的架構概念驗證,提供新一代應用所需的高效能運算。

研發要件:從建模、後摩爾運算到多元多樣的研究團隊

現有的模型功能不夠強大,無法從新型系統定義中模擬與擷取有關元件性能的資訊。因此,我們開發了全新的微縮化建模與模擬技術,目標是超越現行模型的精度與速度。

這些模型本身包含了不同技術模組的特性,這些新型技術量能將能抑制系統微縮的挑戰,涵蓋封裝到運算單元到軟體創新。為了驗證這些模型的成果,我們希望能在系統開發的各個階段建立關鍵技術模組的原型。技術不只有硬體元件,還有演算法、中介軟體、程式設計模型與網路堆疊,一路延伸到軟體開發,以及用戶與裝置的互動。

就基本技術而言,考量現有的矽材技術,例如先進光學I/O與3D製程技術,並探索新興AI演算法與後摩爾時代的替代運算方案。這就囊括量子運算、光學計算設計與超導數位運算,可望在功率效率、運算密度與導線頻寬方面取得超前進展。

模擬與技術方面的挑戰難以解決。但是毫無疑問,研究團隊是最大資產,促使此次研究獲取成果。這批跨域多元的研究人員具備演算法研究、軟體開發、異質整合系統編譯器與中介軟體、微架構以及電路設計等不同背景。他們都渴望且具備能力跳脫框架,希望能帶來富有意義與影響力的全新想法。

(本文為imec提供;作者為Arindam Mallik、Boris Leekens、Eric Mejdrich;編譯為吳雅婷)