2022年IEEE國際超大型積體電路技術研討會(VLSI Symposium),於6月12日至17日在美國夏威夷舉行,吸引了全球多個的研究機構與頂尖大學參與並發表論文。而今年的年度主題為「迎向未來的關鍵基礎的科技與電路技術」,聚焦在對於未來科技演進與應用發展的核心技術。

比利時微電子研究中心(imec)同樣也參加了此一科技盛事,並在會中發表了兩篇極具影響力的論文,以下就是這兩篇論文的重要內容。

埋入式電源軌展開佈線試驗 推動2D與3D IC升級

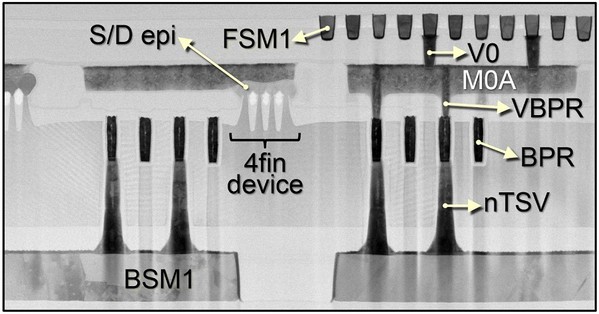

在此篇文中,imec首度展示從晶背供電的邏輯IC佈線方案,他們利用奈米矽穿孔(nTSV)結構,將晶圓正面的元件連接到埋入式電源軌(buried power rail)上。微縮化的鰭式場效電晶體(FinFET)透過這些埋入式電源軌(BPR)實現互連,性能不受晶背製程影響。

這套先進的佈線方案能分離電源線與訊號線的配置,推動2nm以下邏輯晶片持續微縮,還能增強供電效能,進而提升系統性能。此外,imec也在晶圓背面導入了採用2.5D金屬—絕緣體—金屬(MIM)結構的電容,展現更佳的晶片效能。

晶背供電設計能分離邏輯IC的電源供應網路與訊號線,進而減緩後段製程佈線壅塞的問題,還能帶來優化供電效能的好處。

2019年imec首次提出這項技術,不同的製程方案也隨之出現。例如,在2021年VLSI技術研討會,imec首度展示晶背導線互連的實例,將奈米矽穿孔連接到位於晶圓正面的M1金屬層襯墊。

今年VLSI技術研討會,imec在其發表的論文中展示一套進階整合方案,透過埋入式電源軌,將FinFET微縮元件一齊連接到晶圓正面與背面,創下全球首例。

imec的CMOS元件技術研究計畫主持人Naoto Horiguchi表示:「我們相信,從微縮元件與提升性能的角度來看,採用晶背供電設計並導入埋入式電源軌是最有可能實現晶背供電網路的解決方案,這些電源軌在前段製程中埋入晶片,以局部佈線的結構設計推動晶片微縮。」

他接著說明:「我們在開發測試晶片時,從晶圓正面定義埋入式電源軌的圖形,隨後將奈米矽穿孔連接到這些電源軌上,結果顯示FinFET元件性能不受晶背製程影響,這就包含接合目標晶圓與承載晶圓、薄化晶背以及製造深度長達320nm的奈米矽穿孔。奈米矽穿孔以垂直向與埋入式電源軌緊密接合,各穿孔的間距僅200nm,不佔用標準單元尺寸,能確保元件繼續微縮至2nm以下。」

晶背供電設計可望從系統層面提升整體供電效能,尤其目前元件所需的功率密度持續攀升,供應電壓或IR壓降的問題也越來越嚴峻。

imec的3D系統整合計畫副研究主任Eric Beyne表示:「我們在2022 VLSI技術研討會上發表的一篇論文,在晶背製程中導入一顆2.5D柱狀MIM結構的去耦電容。透過這顆2.5D電容,電容密度因此提升了4~5倍,IR壓降現象與無電容(32.1%)及2D電容(23.5%)相比都來得低。這些分析結果來自一套經過實驗數據校正的IR壓降模擬架構。」

Eric Beyne總結:「我們的研究成果顯示晶圓背面具備高彈性的設計空間,還能訴諸全新的設計選擇,解決傳統2D晶片微縮的痛點。此外,我們也展示了一些3D系統級微縮技術的效能,在剝離承載晶圓時,以功能性晶圓取而代之,例如用於3D SOC邏輯元件堆疊的邏輯晶圓,而底層的晶粒可從晶背取得電源供應。」

| 圖一 : FinFET微縮元件透過奈米矽穿孔(nTSV)與埋入式電源軌(BPR)連接至晶圓背面,與晶圓正面連接則利用埋入式電源軌、通孔對電源軌(via to BPR;VBPR)以及電源超出主動區(metal over active;MOA)的結構設計。 |

|

超小型通道生醫感測晶片 同步讀取神經訊號

在這篇論文中,imec發表了一顆具備微縮能力的神經訊號讀取晶片,是目前世界最小尺寸的訊號紀錄通道,可用於神經醫學實驗,同步擷取神經元的局部場電位與動作電位。

該微晶片採用創新的類比數位轉換架構,透過交流耦合一階差量三角積分(AC-coupled 1st order delta-delta-sigma architecture)的調變設計,可以將微弱的神經類比訊號低失真轉換至數位訊號。超小型通道能直接將輸入訊號進行數位化,可望突破現有技術,打造出更高解析度的生物感測工具。

用來開發多通道人機介面的晶片設計要求嚴苛,低功耗和小尺寸成為關鍵挑戰。近期出現了多種創新的讀取電路設計,滿足上述需求的同時,也要顧及像是雜訊抑制、直流電壓偏移校正、輸入訊號範圍等性能考量。

然而,要在這些性能指標之間做出取捨並不容易。直接數位化(direct digitization)的前端電路在靠近訊號源的那端直接將輸入訊號進行類比數位轉換,據研究顯示,這很可能可以大幅減少所需尺寸,但功耗可能居高不下,在頻寬或直流電壓偏移校正方面,效能也有限。

此次發表的神經訊號讀取晶片具備增強型數位化性能,與imec開發的Neuropixels探針相比,展現了更佳的抗躁、功耗與尺寸表現,同時利用交流耦合的差量三角積分調變器,增加訊號感測的動態範圍(dynamic range)與直流電壓的偏移容差。

imec人機介面電路(the Circuits for Neural Interfaces Team)研究計畫主持人Carolina Mora Lopez表示:「此次開發的電路設計成功整合了交流耦合與直接數位化技術,實現接近系統電壓極限(rail-to-rail)的直流電壓偏移校正功能,輸入訊號範圍也增加至43mVpp,勝過其他的交流耦合設計。這些性能至關重要,不僅能避免通道達到飽和,還能容許受到動作或刺激干擾而產生的訊號失真現象。在訊號輸入端採用交流耦合設計還能進一步降低功耗,因為只有交流訊號會進行數位化,因此每通道的總功率僅有8.34 μW。」

差量三角積分架構還能實現數位訊號具備的多數功能,例如抗疊頻失真的濾波功能。因此,利用22nm FD-SOI製程這類高度微縮化的技術,就可能把通道尺寸大幅微縮至0.005mm2,並提升訊號品質。

Carolina Mora Lopez總結:「此次發表的最新電路設計具備微縮化與高度數位化的特色,能夠縮小晶片尺寸並減少功耗,也展現了同步擷取神經訊號的優異性能,為開發更小尺寸的多電極探針鋪平道路,推進神經科學研究發展。」

結語

隨著半導體先進製程推進到2奈米(nm)之後,晶片微縮電路的布線與架構,就成為性能與可靠度的發展關鍵,而imec的論文則為2奈米以下的晶片製程找到了一條兼具可行性與可靠度的道路,讓更高整合度與高性能的晶片成為可能;同樣的,生醫電子也面臨著整合的挑戰,如何把讀取人體微小的類比訊號,並將之進行轉換,也是當前的發展瓶頸所在,而imec所發表的技術,將有望為此帶來全新的視野。(整理/籃貫銘;編譯/吳雅婷)