本文闡述針對現今高度整合CbM解決方案因應EMC標準相容性進行設計時所面臨的關鍵挑戰。EMC的設計頗有難度,即使是電路或實驗室測試設定進行微幅變更都會大幅影響測試結果。本文說明一種系統層級EMC模擬方法或虛擬實驗室,可協助工程師縮短時間內完成EMC相容的設計工作。

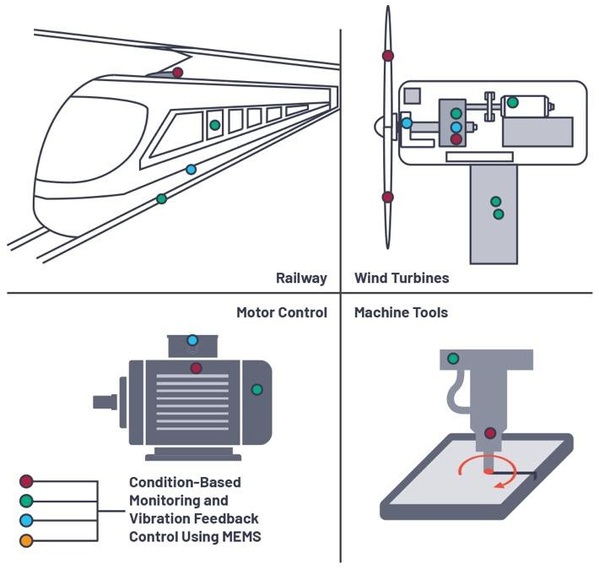

微機電系統廣泛用於鐵路、風力發電機、馬達控制、工具機等環境中,目的是用於監測振動,藉以提升安全性、降低成本、以及盡力提高設備的使用壽命。MEMS感測器的低頻效能,能比其他技術更早偵測出鐵路與風力發電機應用的軸承損壞。大幅節省成本加上對各種設備瑕疵達到更高的偵測率,確保能符合各種嚴苛的安全標準。較寬的頻寬(0 Hz至23 kHz)、低雜訊性能、以及較寬的振動量測範圍(2 g至200 g),這些都是振動偵測的必要條件。而這些目標全都可運用Analog Devices陣容廣泛的MEMS產品輕易達成。

監測振動採用無線通訊系統,用來和各處負責蒐集原始資料的感測器進行通訊,或是利用原始資料執行即時控制。建置有線狀態監測(CbM)系統面臨許多挑戰。其中一項關鍵挑戰就是透過數公尺纜線運行時的電磁相容(EMC)強固性,這類環境會受到包括間接照明電湧、靜電放電、以及像是電感性或電容性負載切換等環境雜訊。

因應EMC擾動能力不良,可能導致從CbM系統收集資料的品質出現間歇性或永久性的衰退,如圖1所示。長久下來,品質不良的資料可能導致對資產健康與維護做出不正確的決策。

| 圖1 : 有線式CbM系統連結振動感測器置於EMC干擾嚴重的工業環境 |

|

本文闡述針對現今高度整合CbM解決方案因應EMC標準相容性進行設計時所面臨的關鍵挑戰。EMC的設計從一開始就極為困難,即使是電路或實驗室測試設定進行微幅變更都會大幅影響測試結果。本文將介紹一種系統層級EMC模擬方法或虛擬實驗室,其可協助工程師在創紀錄的時間內完成EMC相容的設計工作。

為何系統層級EMC模擬非常重要?

現代產品的開發時程包含同步進行的EMC相容設計任務。針對EMC的設計應盡可能無縫銜接,但往往事與願違,EMC問題與實驗室測試經常會讓產品上市延後數個月之久。虛擬實驗室EMC模擬方法協助工程師解決各種EMC問題,其速度遠快過僅採用實驗室測試的方式。

在達成EMC相容性方面,虛擬實驗室模擬方法能解決關鍵問題,原因包括:

‧ 提高現代印刷電路板設計的整合度與元件密度,除了可能導致許多複雜問題,還會衍生許多EMC失效途徑。模擬有助於判斷最佳EMC抑制技巧,而且比光使用實驗室測試的作法更加有彈性與省時。

‧ EMC標準的規範有時含糊不明,意謂若是以不同方法測試電路可能會出現不同結果。相較於實驗室測試,使用模擬方法可迅速變更測試與獲得結果。

‧ 整個系統需要在確保EMC相容性的前提下進行開發,包含選用纜線的種類、長度、遮蔽,以及量測的設定。若是採用模擬法,實際量測時的探針效應就能忽略,而且更換纜線從以往費時數小時大幅縮短至數秒鐘。

‧ 由於各家客戶採用的受測設備不同,可能導致得到不同的測試結果。使用模擬法能更適切地模型分析與瞭解實際客戶應用。

‧ 現有模擬工具並未統一,而且也沒有針對纜線與電路板制定適用的模擬模型。虛擬實驗室除了整合纜線、電路板、以及被動與主動元件模型,還能獲得更準確的結果。

系統層級EMC模擬特性

系統層級EMC模擬透過以下各點特性,能夠加快產品上市時程:

‧ 迅速找出電路弱點,提供針對性建議協助改進

‧ 找出EMC失效以及瞭解失效形成機制,這方面的工作成效能改進99%

‧ 大幅節省成本:無須執行反覆的設計與測試嘗試

‧ 大幅縮短時間:無須反覆嘗試多次設計方案,縮短數個月之久的開發時程,節省包括電路板線路配置、製造、組裝的前置作業時間

EMC挑戰

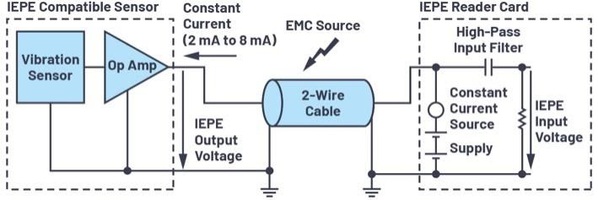

現今高度整合的感測器系統設計經常面臨許多EMC挑戰。首先,現代高整合度電路板設計讓通過EMC測試成為艱難的任務。經常藉由共用電源與資料線架構(幻象電源)的作法來降低系統成本與電路板尺寸(較少的電路板連結)。振動感測器技術廣泛採用的IEPE標準能為振動感測器提供恆定的電流源,並透過同一條線路讀回感測器輸出訊號,如圖2所示。

| 圖2 : 一個雙線式IEPE感測器透過介面連結共用資料與電源架構 |

|

這種雙線式系統意謂電源與資料通訊線會受到相同的EMC干擾,以致在針對EMC進行設計時會額外增加複雜度。EMC濾波元件必須審慎挑選以抑制各種電源干擾,但亦須避免降低資料電路的通訊頻寬。

第二,系統層級EMC標準,像是IEC 61000-4-6傳導射頻抗擾性,針對許多工業產品所制定,製造商會標明產品的抗擾性達到Class A(沒有通訊誤差)或Class B(具有通訊誤差,但系統不必重置)。各家製造商的Class A門檻會有差異,通常以位元錯誤率(BER)或等價的微伏或micro-g來標示振動感測器的功能。

Class A相容門檻通常會極低的電壓,遠低於系統能量測到的最小訊號。傳導射頻抗擾性標準讓使用者能用BER為系統定義通過/失敗標準,以及規範設定細節與雜訊拒斥位準。

最適合設定與BER需要深入探索,同時也成為系統設計者的一大挑戰:如何讓實驗室設計驗證測試設定能因應實際客戶的應用,尤其是當測試設定的微幅變動可能導致測試結果出現巨幅變化。

第三,大多數常見EMC測試程序要求做出整個系統後,再送到EMC驗證實驗室進行測試。全系統包含挑選纜線、長度及遮蔽。不同纜線會有不同的電容規格,可能將更多或更少的EMC雜訊耦合到受影響系統中。纜線長度與遮蔽接地可能導致在高EMC頻率以及不同接地電流返回路徑上出現阻抗不匹配的狀況。

在建構系統時,較理想的測試方法是每個次單元單獨進行EMC抗擾性測試; 然而在實際應用中,整個系統可能受到相同EMC雜訊所影響。這些還只是一部分的原因導致廠方EMC測試很難對比客戶實驗室的測試。

由於現今各種高整合度設計與EMC測試的複雜性,促使業界需要一種能節省時間的彈性設計模式。在實驗室測試之前進行模擬會是解決之道。目前鎖定的目標是在耗費最少的時間與精力下取得正確的實驗室數據。

運用虛擬實驗室加快除錯與解決EMC問題

Analog Devices的系統層級專業與EMC模擬技巧促成虛擬實驗室模擬流程,如圖3所示。虛擬實驗室環境讓用戶更容易首次上手就完成EMC設計,用戶執行的是反覆嘗試虛擬設計,取代費時又昂貴的實驗室設定與反覆量測步驟。運算力、SPICE、電磁場模擬、以及CAD軟體都達到成熟階段,讓這種虛擬實驗室成為可行方案,讓工程師現在可達到前所未有的精準度與模擬速度。電路板、纜線、整合電路晶片與被動元件都能建模分析,以及進行EMC模擬。除了分析結果,還能快速找出電路弱點以及提供針對性建議協助進行改進。

運用虛擬實驗室環境,開發業者在測試過程中可存取系統任何實體節點,不會產生在實際實驗室所面臨的常見量測限制–像是量測設備頻寬、實驗室限制、探棒的非理想阻抗、以及外部雜訊–這些都會對量測產生干擾。

在開始製造電路板之前模擬多項常見工業IEC 61000系統層級EMC標準測試,如表1所示。

表1.常見IEC 61000 工業系統層級EMC標準的模擬

|

IEC系統層級

EMC標準

|

描述與成因

|

模擬

可行性?

|

|

IEC 61000-4-6

傳導射頻

|

電磁場,源自連接到安裝設備整段纜線形成的射頻發射源

|

√

|

|

IEC 61000-4-3

幅射RF

|

工業製程中安裝設備產生的放射性射頻電磁場(像是電動 馬達、焊接機)

|

√

|

|

IEC 61000-4-5

突波

|

由開關或照明瞬態的超壓造成。開關瞬態可能源自電源系統切換,或配電系統的負載變化

|

√

|

|

IEC 61000-4-4 EFT

|

包含繼電器與開關接觸彈跳,或切換電感性或電容性負載時產生的瞬變脈波

|

√

|

|

IEC 61000-4-2 ESD

|

靠近接觸或電場傳導,導致不同電位物體之間靜電荷的忽然轉移

|

√

|

|

EN 50222

幅射性電磁放射

|

設計設備非刻意放射雜訊,可能成為環境中其他設備的干擾源

|

√

|

MEMS與模擬案例研究

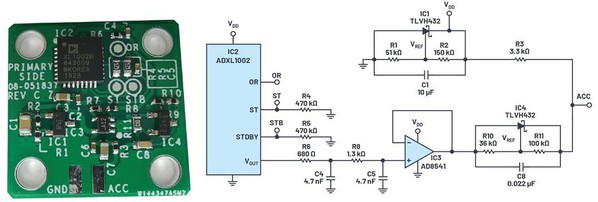

本節介紹模擬案例及與實驗室量測的對比,圖4的振動監測電路中採用Analog Devices的ADXL1002 MEMS加速計,這個電路相容於廣泛使用的IEPE介面,如圖2所示。電路中含有兩個分路調節器,其中一個(IC1)為加速計供電;另外,還有AD8541 運算放大器(IC3),以及第二個(IC4)提供9.5 V 直流偏壓。當系統開始送電而ADXL1002為靜態,通訊匯流排會在12 V dc 進行重置。圖3的電路必須符合IEC 61000-4-6 傳導射頻抗擾性的標準,這項標準是工業應用設備的常見規範。

實際實驗室對比虛擬實驗室模擬,需要多個製程步驟:

1. 實際實驗室設定對比模擬環境

2. 運用虛擬實驗室開發模擬模型(如圖3所示)

3. 運用模擬找出設計中的EMC弱點

4. 使用模擬找出設計問題以改進EMC性能

5. 在實際實驗室中驗證設計以改進EMC性能

關於製程步驟內容敘述如下:

步驟1 真實實驗室設定對比模擬環境

IEC 61000-4-6傳導射頻抗擾性測試適用於在射頻(RF)場環境中工作的產品。射頻場會作用於連到安裝設備的整段纜線。在EC 61000-4-6測試中,射頻電壓從150 kHz 步進到80 MHz。射頻電壓由1 kHz正弦波進行80%的振幅調變(AM)。IEC 61000-4-6 標準規範在10 V/m下Level 3為最高射頻電壓。射頻電壓注入到纜線遮蔽層,或用箝位電路(clamp)進行電容耦合。

如表2所示,虛擬與實際實驗室環境需要對比幾項關鍵參數:

‧ 測試位準與 IEC EMC 標準(振幅,頻率)

‧ 纜線規格(長度、電容、遮蔽)

‧ 系統接地(包括纜線遮蔽)

‧ 量測參數 (電路中的元件與位置)

‧ 測試通過/失敗門檻(振幅、頻率)

表2.實際實驗室設定與模擬環境的對比

|

參數

|

描述

|

對比

|

|

虛擬實驗室

|

實際實驗室

|

|

傳導射頻產生器

測試位準

|

Level 3,0.15 MHz 至80 MHz,10 V/m rms, 以1 kHz正弦波進行80%振幅調變

|

√

|

√

|

|

傳導射頻注入方法

|

100 Ω,6 W電阻,傳導射頻直接注入纜線遮蔽層

|

√

|

√

|

|

纜線

|

雙芯遮蔽線(Belden 4300FE.00100).

1.5 m length. Core/screen capacitance 224 pF/m.

|

√

|

√

|

|

纜線遮蔽連結

|

接地

|

√

|

√

|

|

量測參數

|

在EMC測試過程中,MEMS 感測器PCB為靜態 (沒有訊號擺幅),因此測得的雜訊電壓偏離12V直流額定值。此外,受監視的MEMS電路電源軌是發現電路失效的可靠指標

|

√

|

√

|

|

測試通過/失敗門檻

|

<0.1 % MEMS範圍

(0.04 g 或1.6 mV).

|

√

|

√

|

|

量測設備

|

示波器,電壓探棒.

|

√

不需考量量測設備的影響

|

√

光隔離探棒用來隔離量測設備與傳導射頻雜訊的干擾

|

|

IEPE讀取器/電流源

|

恆定電流源儀表用來作為標準效能量測指標。不同製造商的IEPE讀卡機其雜訊抗擾性會有差異

|

√

|

√

|

步驟2 運用虛擬實驗室發展模擬模型

通常廠商會提供大多數主動與被動電路元件的SPICE模型。電磁模擬器可模擬其他非標準元件,像是電路板幾何與網路,以及纜線模型。

表2所蒐集的資訊協助確保精準模型分析纜線參數。這個系統採用雙芯遮蔽線,成本高於無遮蔽線。沒有遮蔽層讓系統的EMC抗擾性較低。運用無遮蔽線進行模擬,結果顯示EMC雜訊遠多過遮蔽式纜線系統。MEMS IEPE電路,如圖4所示,盡可能設計成精巧尺寸(1.9 cm × 1.9 cm),只有2層PCB電路。使用2層PCB會增加潛在的EMC問題,因為有較高的耦合電容以及串音,因此必須小心設計。

| 圖4 : MEMS 電路採用ADXL1002 與IEPE相容介面 |

|

在這個時間點,系統設計工程師可以開始為PCB與纜線整理出模型,使用電磁模擬工具,將其連接到IC與被動元件的SPICE模型。之後再執行SPICE模擬,以及在系統層級與EMC模擬進行互動。

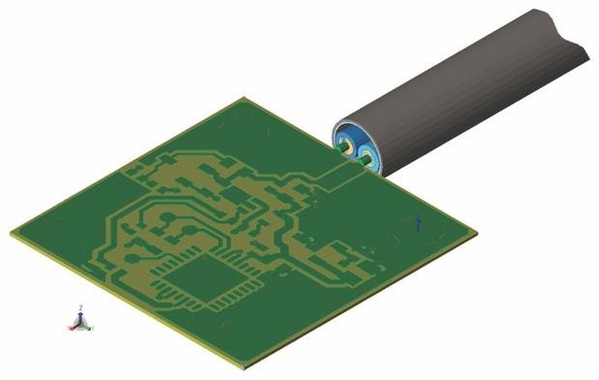

圖5顯示PCB物理幾何與網路以及雙芯遮蔽線的電磁模擬。三維電路板SPICE模型是PCB物理配置的完整抽象模型,包含許多針腳,可用來連結MEMS、運算放大器、以及分路調節器的SPICE模型。透過這種方式,可執行極精準的電氣模擬。被動元件數據(電容、電阻、電感)都可以變更,系統響應可觀察與修改,相較於變更與測試實際硬體的作法,可更快速且富彈性。纜線的SPICE模型也可在測試時進行模型分析–像是纜線長度可以增加或縮減,線長會對EMC耦合與系統效能有顯著的影響。

| 圖5 : 為電路板物理幾何與網路以及雙芯遮蔽線建立的電磁模擬模型, |

|

完成EMC時域模擬後,工程師可分析在不同時間與頻率下的電路瞬態響應。

根據EMC測試的種類,可執行瞬態或頻率分析。許多瞬態分析的案例可用來執行抗擾性測試,另外頻域的案例可用在幅射性電磁放射EMC測試(參考表1)。

步驟3 運用模擬找出設計的EMC弱點

一旦全系統完成模型分析與模擬後,就很容易找出失效機制。EMC雜訊電壓注入到纜線遮蔽層。雜訊電壓之後會耦合到纜線遮蔽層與線芯之間的寄生電容。雜訊會傳導到電路板上的ACC節點,如圖6所示。

雜訊電流會經過最小阻抗路徑,這個案例中會經過運算放大器輸出端的C8電容。運算放大器會飽和,將高電流抽出電源供應器(VDD)節點。IC1 VDD調節器無法供應這麼高的電流; 因此VDD電壓會下降。VDD 電壓降會暫時關閉MEMS感測器(以5V額定電壓供電),導致運算放大器輸出端(雜訊)出現電壓漣波。

第二個失效模式也可找到,這個模式若是只用實驗室測試法就很難甚至根本不可能觀察到以及進行除錯。高頻傳輸線通常會用一個負載作為終端電阻,該負載的阻抗必須匹配傳輸線的阻抗。IEPE纜線由於屬於低頻率(kilohertz)資料通訊,因此通常沒有終端接頭。然而當注入60 MHz到70 MHz範圍的雜訊,由於纜線沒有用匹配負載接上終端接頭,因此雜訊電壓會在通訊匯流排上出現反射。

步驟4 使用模擬為設計找出改進EMC的潛力

目標是判斷成本最小且最有效的電路變更方式來抑制EMC問題。如圖7所示,只須加入兩個電容就能解決兩項EMC問題。22 nF CEMC 會將雜訊帶離敏感線路(運算放大器、MEMS),雜訊電流現在會透過圖中所示的C1電容分流到接地端。鐵氧體磁珠(ferrite bead)在100 MHz頻率下有高阻抗,可加入到電路中作為額外的確保,用來阻隔任何殘除的雜訊。CTERM則會在EMC測試時將高頻率狀態的纜線反射訊號分流出去。

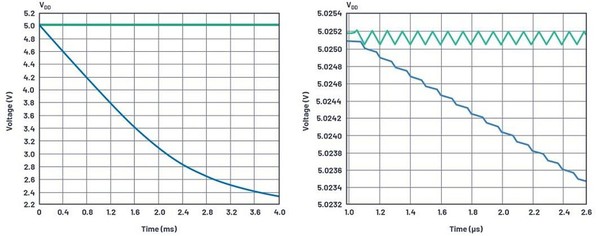

如步驟3所述,VDD 電源網路失效是反映EMC耐受性的一項可靠指標。圖8顯示VDD電源網路的電壓降,這裡沒有使用CEMC。模擬結果預測約2V或更大的壓降。當使用CEMC時,偏離額定值的幅度為微伏範圍,遠低於1.6 mV目標相容門檻。

| 圖8 : 模擬VDD電路網路,包括使用 CEMC 電容(上方綠色波形)與沒有使用 CEMC (下方藍色波形曲線)的狀況 |

|

Analog Devices的ADXL1002 MEMS感測器在11 kHz下具有3 db頻寬,因此選擇CEMC與CTERM變得很重要,選擇正確才能維護11 kHz通訊匯流排。利用虛擬實驗室的彈性,除了可模擬多種電容值,還能挑選出兩個最佳電容值。在加入這些電容後,系統會預測出低於1.6 mV雜訊電壓時通過EMC標準測試的能力。

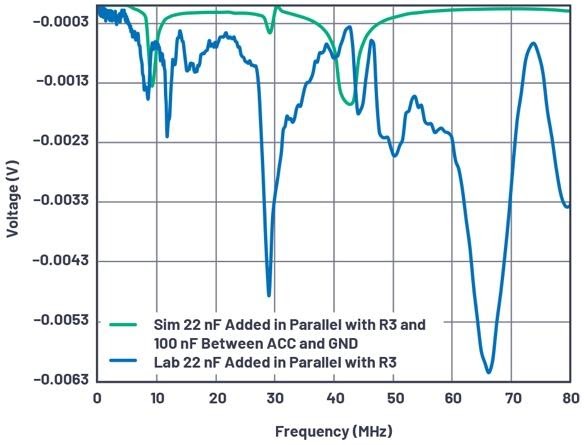

步驟5 在實際實驗室中驗證設計以改進EMC性能

如圖4所示的原始電路使用表2的參數在實驗室進行測試。結果在77 MHz測試頻率下出現912 mV雜訊的失敗狀況。經過步驟4的建議,加入一個22 nF 電容(CEMC)與R3電阻並聯。結果得到99%的改進幅度,量測到的雜訊低於6 mV,如圖9所示的實驗室測試結果(藍色波形)。

為達到低於1.6 mV雜訊的設計目標,在ACC與GND節點之間加入一個100 nF CTERM電容,以及22 nF的CEMC電容。圖9顯示綠色模擬結果,雜訊曲線在0.15 MHz到80 MHz頻譜區間呈現平坦走勢。

| 圖9 : 依循虛擬實驗室的建議進行模擬與實驗室測試的結果 |

|

在達成結果與目標後,就可以判斷系統哪個部分是EMC的弱點。在這個案例中,纜線是主要成因,因為纜線會將EMC能量從來源端耦合到電路,加上因纜線的長度以及較高頻率下的終端阻抗造成的訊號反射。

兩個電容(CTERM與CEMC)能將兩個雜訊源有效分流到接地端。替代的解決方案與方法,像是更換運算放大器,都是不實際的作法。把運算放大器換成超低輸出阻抗的運算放大器則是不理想的選擇,因為輸出阻抗較低的元件天生高耗電,從而影響整體設計的競爭力。

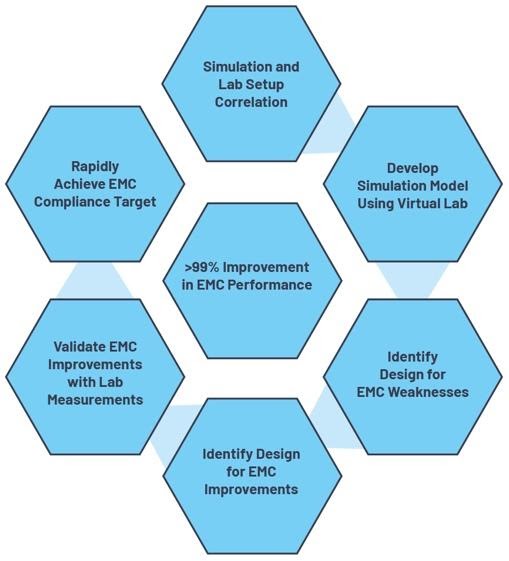

總結

全系統模擬帶來前所未有的洞察力,讓業者掌握在EMC壓力下電路的行為及解決各種複雜EMC問題的最佳辦法。使用這種方法可大幅縮短產品的上市時程。運用本文介紹的製程流程,如圖10所示,可以讓設計的EMC性能獲得超過99%幅度的改進。

| 圖10 : 製程流程,讓EMC性能獲得超過99%幅度的改進。 |

|

(本文作者Ricardo Zaplana1、Richard Anslow2為ADI 1系統應用工程師,2設計工程師)