OLED顯示器的市場熱度持續攀升,在行動顯示與微顯示(micro-display)應用上,一些特定的技術挑戰也隨之浮現。現有的製程,像是精密金屬遮罩(fine metal mask;FMM)與噴墨印刷(inkjet printing;IJP)技術,都還無法滿足新世代顯示技術的應用需求,例如達到更高的解析度與像素密度,或是打造出成像品質充足的透明顯示器。

| 圖一 : 愛美科在OLED顯示器製造技術上發現了重大突破,可望解決次世代行動顯示的技術瓶頸。 |

|

愛美科(imec)證實了光刻技術(photolithography),可望成為克服FMM與IJP技術瓶頸的首選方法,因此,他們將一套全新的製程導入了過往幾乎無人預料到的領域。

行動OLED顯示器的趨勢

OLED正逐漸成為行動手機與手錶的主流顯示技術,這類產品的解析度不太需要再進一步提升,目前落在500ppi以下,可是未來會朝向增加螢幕占比並去除可見機殼的目標發展。因此,整合在螢幕正面的感測器,包含指紋感測器、前置鏡頭等,就需隱藏在顯示器內。要做到這點,就需要一些技術來讓顯示器在不發生影像退化(image degradation)的情況下呈現出透明度。

在其他行動應用中,例如可用於擴增實境(AR)裝置的micro-LED顯示器,像素大小和密度也成為技術考量。目前有好幾種AR眼鏡正處於研究階段,但真正的3D投影還是難以實現。利用超高解析度的2D顯示器,並搭配透鏡陣列(lenslet array),這樣的元件配置就可能製造出成像不錯的立體影像方塊(imaging cube)。

而要實現這點,像素大小必須比現況再微縮一個數量級,也就是3000ppi,甚至是6000ppi。更具體地說,一般手機的像素大小是70微米,那麼目標就是縮至7微米以下,甚至是單一微米等級的尺度。

手頭方案全失效 蝕刻又不被看好

在目前的有機異質電子元件製造中,FMM技術在OLED堆疊中廣獲採用,用來產生發光層(emission layer)的紅、綠、藍像素圖形。因此,解析度高於500ppi的顯示器已經商業化,而且目前還在研發能夠免用FMM的直接圖形化OLED像素,解析度高達2000ppi以上。

然而,這項技術目前有些開發瓶頸,會阻礙採用更大基板並在高階析度下達到更高開口率的發展。舉例來說,在FMM製程中,遮罩可能發生下垂,而直接印刷技術還有遮蔽效應(shadowing effect)的問題。

此外,利用FMM技術的製程方法無法製出孔洞結構;走這條製造途徑還有清洗步驟與替換遮罩的考量,讓產線的運轉成本難以減省。

現在顯示器產業也在研究利用IJP等印刷製程的其他製造方法。多家廠商已展示了150ppi以上的主動式OLED(AMOLED)元件。這些製程受到業界肯定,因為它們不受基板大小限制。

另外還有幾項研究的目標是提升印刷的解析度,例如氣溶膠噴塗(aerosol jet)或是靜電噴霧(electrostatic jet)印刷技術。不過目前都還要面對一些技術挑戰,像是大面積沉積時元件層的厚度均勻度問題,還有這些元件與採用蒸鍍製程的OLED相較,可靠度較低。

過去有很長一段時間,業界並未將蝕刻技術納入考量。具體來說,OLED堆疊先前被認定無法在複雜且嚴峻的製程環境下正常運作。就以OLED的材料敏感度為例,就包含了濕度、氧氣、UV光照、有機溶劑和電漿表面處理等考量因素,這些都是標準蝕刻流程的一部份,但也都有可能會導致OLED元件發生不必要的衰減。

新i-line蝕刻製程 產出業界相容的OLED像素堆疊

歷經數年的持續努力,藉由多方合作與內部團隊的領域專長,愛美科成功開發出新的i-line(365nm)蝕刻製程,能夠產出與業界相容的OLED像素堆疊,而且沒有什麼基本限制,不論是對行動顯示器的基板大小,或是對微顯示器採用8吋(200mm)或12(300mm)吋晶圓尺寸,皆無設限。

這些成果源自於多方面的整合優化,包含元件結構、光阻劑和製程環境。確切來說,愛美科在2020年12月國際顯示技術研討會(the International Display Workshops)上展示了兩大成果。

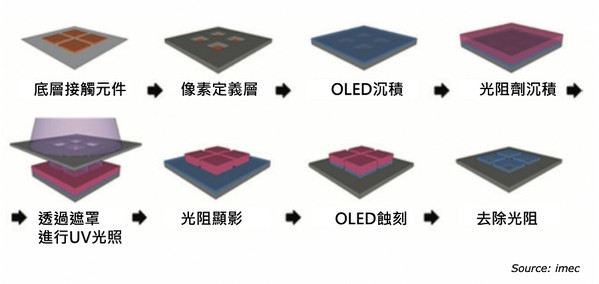

| 圖二 : 愛美科展示了如何在OLED製程中導入蝕刻技術。 |

|

首項成果是打造出像素大小為10μm、間距為20μm的圖形化元件,而且在電致發光(electroluminescence;EL)的光譜與元件壽命方面,這些元件和非圖形化元件相比並無衰減。唯一測到的衰減發生在連續蝕刻步驟之後,那就是驅動電壓增加了。

在發光亮度為1000nit的情況下,該元件的驅動電壓約為6.6V,但其實應該降至3.8V才是比較能夠接受的範圍,這也是FMM技術的基準點。然而,該元件的驅動壓在進行第一次蝕刻後會增加,而且在進行第二次蝕刻後維持穩定,這可能表示,衰減現象會發生,是因為有機半導體元件上方的光阻劑在蝕刻過程中直接曝光。這個可能也提供了研究人員一些有用的研發見解,並為進一步優化指明一條可行的發展途徑。

第二項成果則是展示功能性OLED堆疊的高解析度孔洞陣列(hole array),能夠用來實現螢幕內嵌感測(in-display sensing)技術。在第一階段,愛美科製出具備完整孔洞陣列的測試結構,而研究結果顯示,元件表面的開口率高達81%,而透明度則依照製程選用的材料不同,可以增加20%~70%。

進入第二階段時,這些孔洞可以在OLED功能元件內部成形。元件特性在孔洞生成的前後並沒有顯著的衰減現象,除了先前所說的驅動電壓會微幅增加,不過也僅高出了0.6V,這個程度對OLED像素製程來說其實相當低。

就產業相關性而言,這些研究成果不容小覷。有些輕鬆點的應用場景僅需使用單色顯示,而且驅動電壓不成問題,這套方案就能考慮納入產業應用。同理可推至其他只需進行單次孔洞陣列圖形化步驟的應用。

針對要求低驅動電壓的全彩行動顯示應用,或是需要更複雜孔洞結構的顯示器製造場景,目前還需要深入研發。不過,現在的這些成果是相對少數的研究團隊和組織的心血,如果有更多的產業要角加入,後續發展可以加速進行。產業價值鏈中的材料、設備、製程和元件廠商,都將對這項技術邁向成熟的商業應用發揮作用。

從1970年首度亮相的5微米CPU,到最新一代iPhone的5微米晶片,半導體產業花了半個世紀達成。偕同研究夥伴,愛美科花了不到五年就將OLED像素尺寸從20微米微縮至10微米,目前也已經能打造出3000ppi的白光OLED顯示器。

為了研發出6000ppi甚至更高解析度的OLED顯示器,約在1微米的像素大小必需實現。在OLED顯示領域進一步展開光刻技術的合作開發,可望能讓這個目標更趨近於現實。

(本文作者Tung-Huei Ke為愛美科研發主任;編譯/吳雅婷)