在過去數年的時間,半導體的2.5D異質整合晶片的確解決了很多半導體產業發展上所遇到的挑戰,包括舒緩摩爾定律的瓶頸,還有在降低一次性工程費用 ( Non-Recurring Engineering;NRE ) 的同時,還能提供高階處理能力,並且還能提高產量以及縮短產品上市時間。

小晶片生態系統成形

隨著半導體技術不斷的發展,在技術上其實已經不太是個問題了。特別是近年來先進製程的開發不斷傳出新的捷報,在摩爾定律的瓶頸上似乎又被工程界不斷開發出新的道路。因此看今天的半導體發展,技術並不是個太大的難題,主要的問題在於一個全新商業模式的形成。

在今天的半導體業界,許多大型企業為了加速晶片整合速度,以及提升半導體密度,因而使用了2.5D晶片。事實上進一步觀察這些廠商的規模,已經足以走出一條自己的路,並開創出一條自己的半導體小晶片(Chiplet)生態系統。

至於不到那麼大規模的半導體企業,最大的挑戰仍是在於現成小晶片設計上的可用性,例如透過這種方式去發展出異質整合晶片(Heterogeneous SoC;HSoC)。如果不是透過小晶片的方式來發展異質整合晶片,其初始HSoC開發的NRE費用將可能會比傳統SoC還更昂貴。

持續實現獲利

事實上,在半導體製造中的真正革命,所需要的是小晶片的有效商用市場。少了這樣的小晶片生態系統,小晶片和異質整合晶片仍將永遠是大型半導體製造商的專屬領域,一般中小型半導體廠商根本沒有能力跨入。此類市場的關鍵是適當的庫存、兼容性、資料文檔和可測試性。儘管如此,對於任何的商業實體來說,其實都需要一條更明確的途徑來實現持續的獲利,特別是半導體產業這種動輒花費高額成本的燒錢產業。

小晶片的推動需要生態圈中許多不同的角色的參與,而建立小晶片市場的起步,非常需要一個推動的力道,這裡所指的力道,其中很關鍵的要素是大量的初期投資,來使小晶片的計畫啟動。在新興市場中,特別是半導體市場,任何先行者都將會面臨著許多不確定性。因此市場的推動者必須準備一筆大量的投資,並且願意冒險。基本上,一個強有力的技術推動者(講明了就是一個龐大的財團),很可能正是帶領這種新技術典範起飛的關鍵。

異構3D封裝系統

3D整合和封裝技術的進步,現在使得在包含多種技術小晶片的單一封裝中構建複雜的系統成為可能。

從歷史上看,由於功率、性能和成本方面的考慮,高級整合使用整體式設計來實現。透過包裝和堆疊技術的創新,設計人員可以將其系統與小晶片整合到單一封裝中,這些小晶片可以使用所選定的製程技術來優化特定功能。

新興系統要求以極小的接口功率來實現非常高的互連頻寬。實現這一目標的兩個關鍵要素:包括超短距離接口標準和3D整合封裝技術。

先進介面匯流排AIB

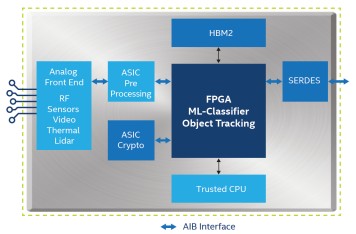

| 圖一 : 可能的異構系統封裝範例,該系統使用AIB作為接口將感測器、ASIC、FPGA、CPU、記憶體和I / O串連在一起。 |

|

英特爾的先進介面匯流排(Advanced Interface Bus;AIB)技術,是晶片對晶片的PHY級別傳輸標準,可透過Chiplet的IP庫來實現模組化的系統設計方法。

AIB使用類似於DDR DRAM接口的並行數據傳輸機制。AIB與製程和封裝技術無關,例如英特爾的嵌入式多晶粒互連橋接(EMIB)或台積電的CoWoS等封裝技術。英特爾現在提供免版稅的AIB接口授權,以支援廣泛的小晶片設計、服務提供商、代工廠、封裝和系統供應商等生態系統。

打造小晶片生態鏈

許多主要的大型半導體供應商,例如英特爾、AMD、Marvell,還有一些具有規模的系統公司(例如思科)都正在投入開發HSoC異構系統,這些科技大廠基本上特性並不相同,而他們投入開發異構系統通常也出於不同的原因。

例如英特爾可能就是這種異構技術的最大採用者,且至少已經投入發展幾種不同的異構產品線。例如透過異構技術來打造出最佳化的處理器產品,以及在FPGA產品線上,透過異質化的架構來完備其FPGA架構,使其FPGA可以允許更高速的運算處理。

至於AMD則是透過異構設計來提高晶片的產量,並允許將重點發展的產品透過最為最先進且最昂貴的7nm製程技術來生產。而思科之所以採用異構設計,是因為它們的系統已經變得非常龐大,透過異質架構才是最適合的發展方式。

在所有的這些情況下,工程團隊都在解決非常特定的問題,儘管這些問題不一定會通用到足以被廣泛採用。我們可以發現,透過小晶片的使用,讓他們能夠將產品推向市場,而且這些產品比起競爭對手的商品還要更有競爭優勢。為了避免競爭對手也獲得相同的技術,進而推出相似的競爭產品,這些小晶片的供應商不太可能與其他廠商共享小晶片技術。

結語

在這樣的商場現實之下,未來主要的半導體公司都將繼續按著自家私有的小晶片生態系統發展道路走下去。儘管英特爾在幾年前推出了先進介面匯流排AIB標準,正是針對小晶片之間的相互連結而打造,目前Intel也陸續推出了更新一代的EMIB封裝標準,然而其他小晶片廠商的採用度還有待觀察,在採用上還存在諸多考量(一般認為多半都是出自於各自的利益使然),這樣的考量也使得小晶片生態鏈的發展受到了些許限制與阻礙。

**刊頭圖(source:intel.com)