電源管理創新技術如何實現超大規模資料中心的人工智慧應用

挑戰

人工智慧 (AI)、智慧城市及自動駕駛,是影響人類及改變生活型態的其中幾項重大趨勢,也在許多相關領域對現有先進技術造成艱困挑戰。

電源管理是在雲端採用 AI 技術,同時繼續滿足計算和儲存需求的最大瓶頸之一;具體而言,問題在於系統向處理器及 ASIC 供電時,電源轉換器的功率密度。

「開放運算專案」(OCP) 嘗試訂定電源架構的全新標準,以因應前述挑戰;其中將傳統 12 V 的中間匯流排電壓提升為 48 V,以大幅降低傳輸損耗,並以更優異的效率傳輸電力至酬載 (亦即 AI ASIC/GPU/CPU 或 SOC)。AI 加速器模組的功率位準已經超過 750 W,電流最高可達 1000 A (0.75 V 核心電壓情況下)。如果一塊主機板上最多要裝設八個這類模組,功率額定及熱管理就是一大問題。

現有先進技術

導入 48 V 輸電架構之後,提升電源轉換程序效率就非常關鍵。雙級轉換常用於滿足高電壓比率需求,以及因應困難的暫態需求。LLC 諧振轉換器普遍作為中間匯流排轉換器 (IBC),因為其中可在 48 V 一次側提供零電壓切換 (ZVS),並在 12 V 二次側提供零電流切換 (ZCS)。如果不需要隔離,可調整以轉換為基礎的開關電容轉換器 (ZSC),進一步提升效能及功率密度。

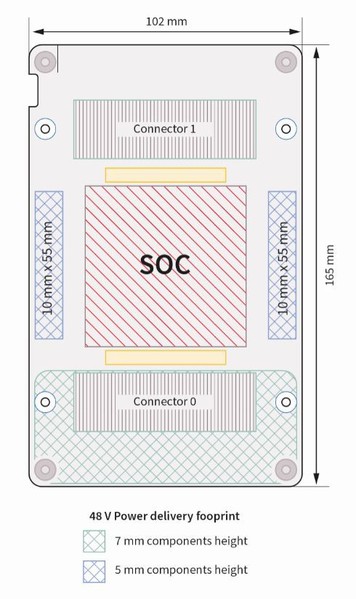

至於圖 1 所示的新型開放運算加速器模組 (OAM),功率密度不但是其中的關鍵參數,也是新型 48 V 輸電架構的主要挑戰。圖 2 顯示 IBC 及多相降壓系統可用的空間區域。

為了滿足空間需求,第一級和第二級都需要使用高頻切換運作。不過高頻運作會增加損耗 (亦即切換、閘極驅動及傳導損耗),特別是 VRM 級 (亦即 1.5 至 2 MHz)。

如果將 VRM 級的輸入電壓降低為 6 V,就可減少空間尺寸同時維持高效率。在轉換率更高的情況下,以開關電容拓撲為基礎的 IBC 就過於複雜龐大,原因包括需要因應浮動驅動器需求,以及開關和陶瓷電容器數量。

高降壓比 IBC 普遍使用全橋 LLC 諧振轉換器等變壓器型拓撲,不受電氣隔離需求影響。使用變壓器型拓撲有許多優點,但也有缺點。

| 圖2 : 48 V 輸電系統的 OAM 尺寸及空間需求 |

|

舉例來說,降壓比是由一次側及二次側之間的繞組匝數比決定,而銅在 LLC 中心分接諧振轉換器中的使用率並未最佳化。為了克服 I2R 損耗在變壓器中的限制,英飛凌推出混合開關電容 (HSC) 轉換器,結合開關電容轉換器及高降壓比磁性裝置的各項效益,透過電容器及磁性裝置傳輸能量,大幅提升效率及功率密度,實現 OAM 所需的功率密度。

HSC 轉換器

在 LLC 等諧振轉換器中,切換頻率需要接近 LC 諧振以提供軟切換。此外由於所有能量是透過變壓器傳輸,因此會增加整體損耗。轉換器拓撲效率如果因為元件不符而大幅變化,在沒有額外補償措施的情況下將無法量產。為了克服前述問題,英飛凌提出以 HSC 拓撲雙相諧振轉換器為基礎的全新方法。如圖 3 所示,HSC 是由分為兩段的 6 個 MOSFET 組成,透過兩個飛馳電容器及名為多重分接自耦變壓器 (MTA) 的磁性裝置連接;MTA 則是由 4 個串聯繞組連接,共用相同磁芯。ZVS 及 MTA 磁性電感可實現高頻運作。

HSC 提供未調節電壓軌,取決於 N_1 及 N_2 之間的匝數比。拓撲是由兩個對稱 PWM 驅動: H (亦即 Q_1,Q_3 and Q_5 為 ON 且 Q_2,Q_4 and Q_6 為 OFF) 和 L (亦即 Q_1,Q_3 and Q_5 為 OFF 且 Q_2,Q_4 and Q_6 為 ON)。狀態之間導入的停滯時間,可讓 ZVS 運作不受負載影響。HSC 可在諧振頻率之上或之下運作,不會影響 ZVS 運作,因此可維持高水準的整體系統效能,不受元件容差影響。

HSC 能夠達到高效率及高功率密度的關鍵要素之一,就是使用品質因數 (FOM) 更理想的低電壓額定 MOSFET。例如以 48 V 電軌運作的 8:1 組態,就可使用 Q_3 及 Q_6 的 25 V 額定 MOSFET。

源極向下概念推動功率密度向前突破

為了因應功率密度的種種挑戰,必須在元件層級有所創新,推動諧振拓撲持續進展。英飛凌推出源極向下 (Source Down) 封裝技術後,IQE006NE2LM5 可進一步提升電氣及熱效能,滿足現代資料中心應用所需的功率密度。這項創新封裝的主要效益包括:

--降低 30% RDS(on),減少 I2R 損耗

--降低封裝相關寄生效應,減少 FOM 進而降低切換損耗

--降低 Rthjc,以最佳方式分佈封裝產生的熱能

--導熱片置於源極針腳附近,可實現最佳化配置,讓大面積的接地區域作為散熱器

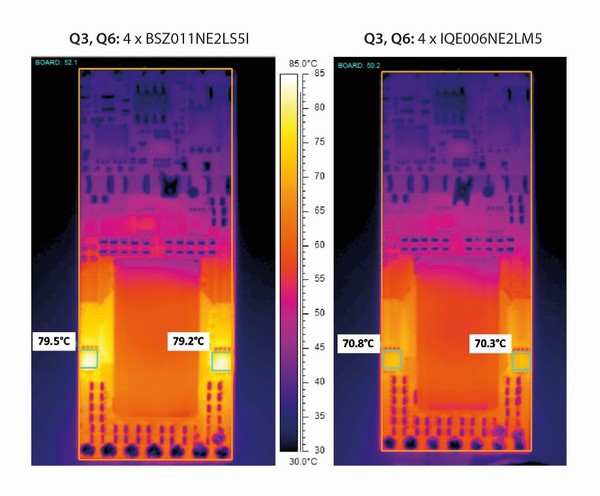

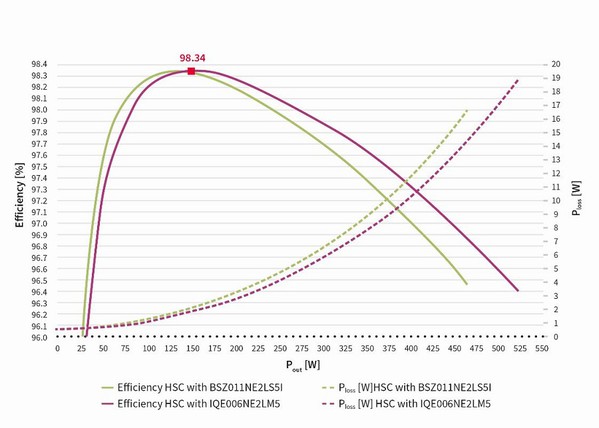

為了比較效能效益,建構了兩種版本的 8:1 HSC,其中一個主機板使用現今標準的汲極向下 (Drain-Down) 裝置 (BSZ011NE2LS5I),另一個則使用源極向下裝置 (IQE006NE2LM5), 圖 4 顯示裝置之間的熱效能比較結果。傳統封裝顯示的熱點 (圖4a),可在使用新型源極向下封裝後 (圖 4b) 消除,大幅改善 MOSFET 表面溫度,與汲極向下裝置相差攝氏9度。圖 5 顯示效率比較結果 (包括輔助損耗),其中新型源極向下裝置的系統效率較高,也讓功率密度大幅提升。

| 圖4 : HSC 在 450 W 使用 48 V 輸入,在Tamb =攝氏24度和 v=3.3 m/s 條件下的熱行為:(a) 使用 BSZ011NE2LS5I、(b) 使用 IQE006NE2LM5 |

|

| 圖5 : 48 V 至 6 V 的 HSC 轉換器效率 (包括輔助損耗),其中使用 BSZ011NE2LS5I (藍色) 及 IQE006NE2LM5 (紅色) 。條件為Tamb =攝氏24度和 v=3.3 m/s |

|

綜觀前述所有效益及效能測量結果,顯然源極向下封裝技術的創新解決方案,是滿足所需功率密度的關鍵因素,以便供應人工智慧等重大趨勢所需的大量電力。

(本文作者Bastian Lang1、Roberto Rizzolatti2、Christian Rainer3為英飛凌科技1產品行銷經理、2-3系統創新工程師)