科技的持續進步促使所有電子系統的功能日新月異,但產品內部的可用空間卻也不斷地縮減中。以手機而言,其內部整合了觸控螢幕、閃光燈、省電模式、以及精密攝影機等元件。汽車儀表板方面,過去只有基本的調頻收音機和幾個指針式儀表,如今則裝滿各種精密儀表、衛星收音機、藍牙、GPS、手機連網、多色照明、以及眾多USB連結埠。各種強固型工業電腦則是配備包括條碼讀取器、大型螢幕、機械硬碟機、以及背光鍵盤等組件。醫療電子裝置則有感測器、多強度閃光燈、儀表、以及各種省電模式。

然而恒久不變的一點,則是對電源的需求。可攜式與系統電子功能持續增加,對於供電的需求也水漲船高,尤其是用到以下精密數位IC時:

--繪圖處理器(GPU)

--現場可編程邏輯閘陣列(FPGA)

--微控制器與微處理器

--可程式邏輯元件(PLD)

--數位訊號處理器(DSP)

--特定用途積體電路(ASIC)

這些複雜數位裝置需要多軌式高功率密度電源供應器,同時具備高電流、低電壓、快速瞬態反應等特性。這些嚴苛要求加上特定高效能需求 – 包括如低雜訊或數位控制 – 對電源供應器開發業者施予極大壓力,必須推出尖端性能的解決方案,上述元件的種種進展促使電源供應器的研發業者必須跟上發展的腳步。

電源系統的各種設計挑戰

現代電子系統研發業者面臨重重挑戰,包括受限的空間、有限的工作溫度範圍、以及雜訊方面的規範。為節省電路板空間以致必須提高整合度,因此也需要高效率的電源元件以便壓低溫度。

舉例來說,現代的汽車儀表板裝滿各種電子系統,而且必須在甚高的環境溫度下工作,以致溫度監視與通報成為其關鍵的要求,特別是電源管理元件。系統控制器除了回報過溫(OT)警訊,還會執行各種紓解步驟防止系統過熱,像是關閉較不重要的功能以調降處理器、螢幕,以及網路通訊等元件的效能。

在電源供應器方面,即使是最基本的車載資訊娛樂中控儀表板也需要供應多個低電壓電源軌(輸出電平),總電流須達到數安培之譜; 而高階車款搭載的中控台則需要規格更高的電源供應器。綜觀傳統的作法,低電壓供電軌是由多個微小的負載點(POL)分立式電源調節IC,或是由高整合度的大型電源管理IC(PMIC)來產生。許多PMIC產生的供電軌甚至多過實際需要數量,且佔用電路板空間甚多,因此可以調降某些供電軌的供電來因應,但這也會讓最初的整合變得沒有意義。

另一項潛在的設計挑戰是功能疊加(feature creep),或是在開發過程中緩步變更產品規格 – 進而改變輸入與輸出電壓以及輸出電流。功能疊加有可能全盤推翻原先選用的IC以及相關的分立元件。

在最好的情況下,若是在電路板設計完成後又再變更系統規格,這時可藉由更換可調式輸出轉換器上的幾個電阻來調整電壓。但是在最糟情況下,若是更新後的電流值超過原用轉換器的切換電流額定值,就必須把多顆IC更換成針腳不相容的IC。如此一來,就必須重新進行IC、機板、甚至系統層級的驗證,因此就算功能變更的幅度再小,都會大幅增加成本以及拖延開發時程。

想要解決這些問題,電源IC的輸出規格必須超越單純分立的單一或雙輸出IC,而且佔用空間必須更小,成本也必須低於全功能式PMIC。這種介於兩個極端之間的調節元件屬於多重輸出的電源IC,能以可調整數量的調節供電軌,而且解決方案佔用的電路板空間也比較小。在理想狀況下,這樣的IC應能輸出大範圍電壓與電流,以因應開發過程中供電需求的變化,省去重新驗證的流程,以及縮短產品的上市時程。

此外,解決方案必須在高於5V的輸入電壓下工作,並發揮高效率,藉以應付各種類型應用,像是接上12至18V的牆式電源轉接器。其他要求的功能特色,還包括整合式安全與監視功能、大範圍的工作溫度、以及創新的封裝設計與高溫度效能等。

高彈性可設定20 V多輸出電源IC

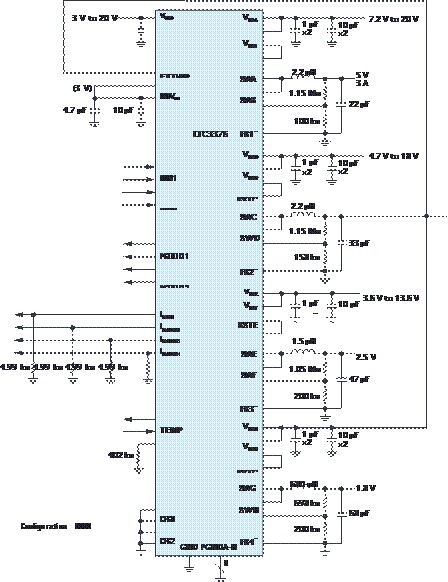

ADI旗下Power by Linear LTC3376 為一款高整合度通用型電源管理解決方案,主要鎖定需要多個低電壓電源軌的系統。這款元件能由客戶自行設定,從一個最高20V的輸入供電,匯出1到4個獨立的調節輸出供電,支援15種輸出電流組態,總輸出電流最高可達12安培(參見圖一)。如此高彈性讓 LTC3376適合各種不同的多通道應用,其中包括電信、工業、汽車,以及通訊系統。

LTC3376 結合4個獨立降壓穩壓器通道,以及8個可設定1.5安培供電級,搭配彈性定序與故障監視,可用輸出電流達到12安培。LTC3376的尖峰降壓效率為96%,所有通道的輸出電壓精準度達到正負1%。每個通道可供應3至20V的獨立輸入供電,輸出電壓範圍最低可達0.4V。相鄰輸出通道可與一個共用電感並聯,藉以簡化電路。直流對直流轉換器可透過調整CFG0 至CFG3針腳,設定成15種供電組態。此外,這種設計不需外部鈦酸鍶鋇(BST)電容,因為BST電容已經整合在元件封裝內。

LTC3376的切換式穩壓器的工作模式有兩種: Burst Mode操作(啟動預設模式)用來在輕負載時達到更高的效率,以及強制連續脈衝調變(PWM)模式,用來在輕負載下降低雜訊。切換式穩壓器採用內部補償機制,只需外部回饋電阻就能設定輸出電壓。降壓穩壓器有限制輸入電流的軟啟動機制,能限制開機時的流入電流;差動輸出感測、以及短路保護等機制。此外,元件還內含可設定與可合成的1 MHz至3MHz振盪器,預設切換頻率為2 MHz。

所有4個轉換器的靜電流只須42 μA就能啟動。其他特色還包括: 4個power good針腳,顯示已啟動的直流對直流轉換器落在目標輸出的規範比率範圍;電流監視器用來對每個降壓負載執行外部監視;一個EXTVCC 針腳用來提升效率;精準RUN針腳閥值用來執行啟動定序;晶粒溫度監視器輸出(可透過TEMP針腳上的類比電壓來讀取)顯示內部晶粒溫度;過溫功能,用來關閉超載(overload)時晶粒溫度過高的降壓元件。

LTC3376提供微型化64球 7 mm × 7 mm 覆晶球狀閘陣列(BGA)封裝。其中E與I等級的元件代表的是接點工作溫度範圍攝氏零下40度到攝氏125度的元件。

彈性與可設定能力

LTC3376具備的彈性讓它能設定成15種不同的輸出組態:

--單電感、單輸出12安培降壓穩壓器,所有供電級都在內部聚集以產生最大的輸出電流。

--4種可能的2 buck組合,包含2個電感,總輸出電流達到12安培

--5種triple-buck組合,每種組合12安培,搭配3個電感

--5種quad-buck組合,每種組合最高12安培,搭配4個電感(參見圖二)

圖三顯示15種可能的輸出組態。這樣的彈性讓用戶在設計過程中遇到需求改變時能夠輕易做出調整 – 不需要驗證新IC,同時繼續延用LTC3376。

| 圖三 : LTC3376:15個12安培總輸出電流組態的例子 |

|

卓越的散熱設計與精小解決方案

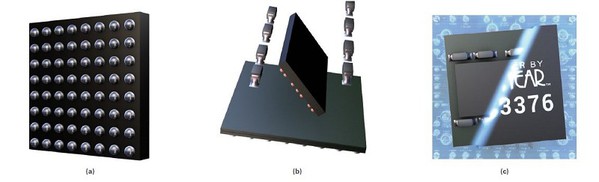

LTC3376造就出一個高散熱效率的精小解決方案,混用多種封裝技巧,構成64球的7 mm × 7 mm覆晶球狀閘陣列封裝。內部封裝結構採用銅柱取代打線。內部的升壓電容以及整合基板接地面能進一步改善電磁干擾 – 電磁干擾受到電路板佈線的影響相對比較小 – 因此能簡化設計流程並降低效能風險(參見圖四)。此外,在晶粒內部,電源元件經妥善配置以提高散熱效果 – 讓功率消耗平均分佈。

| 圖四 : LTC3376 覆晶封裝搭配 (a) 球狀閘陣列 (b) 晶粒底部的銅柱 (c) 內嵌旁路電容 |

|

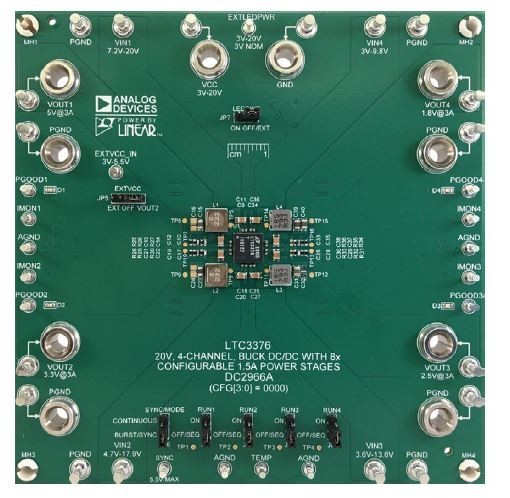

圖五顯示一個完整LTC3376解決方案,組成quad 4 × 3 A 降壓 (總輸出電流為12 安培)組態。注意到整個解決方案的尺吋有多麼精小:工作區域僅約1.5 cm × 2.9 cm大約還不到4.4 cm2。

| 圖五 : LTC3376展示板為一款4 × 3 A 降壓解決方案,可輸出5 V、3.3 V、2.5 V、以及1.8 V等電壓 |

|

額外的系統監視、安全、以及保護功能

除了可設定外,LTC3376還內含多種安全功能以監視與保護被供電的系統。系統會透過每個降壓元件的PGOOD針腳來通報各種供電故障狀況。每個降壓穩壓器都有一個電流監視器,會在IMON針腳產生一個電流,電流值會和降壓元件的平均負載電流正比例。

為防止高溫對LTC3376以及週圍元件造成損壞,LTC3376還整合過溫保護功能。當LTC3376晶粒溫度達到攝氏165度(額定值)時,所有已啟動的降壓切換穩壓器都會關閉,並一直維持在關閉狀態,直到晶粒溫度降到攝氏155度(額定值)為止。

此外,LTC3376還內含一個溫度監視器:透過對類比TEMP針腳電壓進行取樣,即可讀出晶粒溫度。TEMP針腳電壓代表的溫度T其計算公式為:

T=(VTEMP/10mV)x1℃ (1)

此處的VTEMP 為TEMP針腳的電壓。

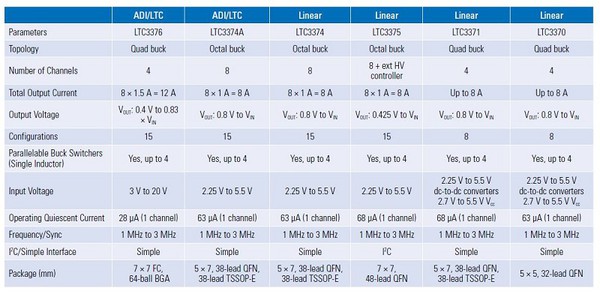

可設定降壓穩壓器系列

圖六顯示整個系列的可設式quad與octal buck穩壓器,此系列的新成員為LTC3376。LTC3376的最高輸出總電流(最高達12安培),以及最高輸入電壓(最高到20V)。

| 圖六 : ADI旗下Power by Linear 系列元件可設定成4通道與8通道降壓穩壓器 |

|

總結

技術的進步促使汽車資訊娛樂、消費性掌上裝置、工業設備、以及醫療裝置的功能不斷增加。在許多例子中,這些系統功能的輸入電壓超過5V,供電的元件包括精密低壓/高電流數位IC,這類IC有自己獨特的供電需求。以往的電壓軌與電流都是由多個分立式電源調節IC、或相對較大的整合式電源管理電路或是PMIC來支援,但兩者都無法提供彈性與精小的尺吋。

運用單一4或8輸出電源IC來取代這些解決方案,會是一個更明智的選擇。LTC3376針腳設定PMIC即是這種新世代多輸出電源IC。它是一款20V輸入、數位可設定、高效率的多輸出電源供應IC,內含4個同步降壓轉換器,以及8個內部供電級(IOUT 輸出電流最高到12安培),擁有低輸出電壓的能力。

由於可能有15種不同的輸出電流組態,系統開發業者可利用其彈性,減少電源模塊系統變更與功能疊加造成的影響。結果是排除所費不貲且費時的機板或系統層級重新驗證、縮短產品上市時程、降低研發成本/升級時間/各項成本。

(本文作者Steve Knoth為ADI 資深產品市場經理)