本文介紹一個Simulink模型,可做為設計無線收發器及建立無線網路的基礎架構。這個無線收發器包含PHY層與MAC層。藉由使用通訊工具箱、事件模擬模塊組附加的功能模塊,可以將Simulink模型延伸運用到更先進的無線收發器上,如WLAN、V2X與無線IoT。

本文介紹一個Simulink模型,可做為設計無線收發器及建立無線網路的基礎架構。這個無線收發器包含了實體層(physical layer;PHY層)與媒介存取控制層(medium access control layer;MAC層)。而無線網路的模型是由多個在衰減通道(fading channel)進行溝通的無線收發器所構成。

我們使用了一個QPSK調變的簡易PHY層,以及兩種可選擇的MAC層協定:以ALOHA為基礎的隨機補償(ALOHA-based random back-off)和CSMA/CA(IEEE 802.11)。為了讓說明比較容易,我們省去一些常見於無線收發器的模塊,像是交錯、加密與通道編碼。

你可以使用這個無線收發器模型來研究PHY與MAC行為、PHY與MAC之間的互動、或者研究整個網路。你也可以將它做為一個模板,利用通訊工具箱(Communications Toolbox)、無線區域網路工具箱(WLAN Toolbox)、事件模擬模塊組(SimEvents)內的工具和演算法來設計如WLAN、V2X與IoT等更複雜無線收發器的模板。PHY層模塊與MAC層的事件導向系統模擬軟體(Stateflow)圖表都讓你能夠透過硬體描述語言轉碼器(HDL Coder)產生HDL程式碼,並且以包含了SDR(AD9361)與FPGA(XilinxR ZynqR-7000 SoC)的ADI RF SOM板作為目標硬體來即時實現無線收發器。

網路架構

這個Simulink模型的頂層是由一個衰減無線電網路模塊與幾個無線收發器節點所構成(圖1)。這些節點以ad hoc的方式溝通:網路中任一個節點皆可發射訊號至其他節點,也可以從其他節點接收訊號。這個無線收發器半雙向(half-duplex)模式運作。在網路架構裡面,每一個收發器節點的輸出可到達其他收發器成為輸入。依無線電通道的互換原則,每兩個節點之間的兩條通道設定必須相同,而不同對無線收發器通道的通道設定可以不一樣。

在無線收發器的設計,PHY層模型是以接近真實硬體實現的Simulink模塊所建立。MAC層的模型則是透過Stateflow來反映現實中有限狀態機器的特性。

封包資料架構格式

這個無線收發器所使用的封包資料架構格式與 MATLAB範例:Packetized Modem with Data Link Layer定義的格式相同。如圖所示,PHY的表頭資料共有4個區塊,這裡負載長度(Payload Length)表示了資料連結單元(Data Link Unit)的總位元長度,並且由Header CRC覆蓋。而MAC的表頭資料有七個區塊,架構CRC(Frame CRC)覆蓋了MAC表頭資料(MAC Header)和架構主體(Frame Body)。架構有兩種:資料架構(Data frame)與認可架構(Ack frame)。認可架構的架構主體長度為零。資料架構與認可架構都有如同在IEEE 802.11所定義的格式。

我們現在來更仔細地查看頂層Simulink模型的每一個元件。

無線收發器

無線收發器節點模型使用了半雙向(half-duplex)的Tx/Rx模式(圖3)。

它由一個PHY層、一個MAC層、一個邏輯鏈路控制(Logic Link Control;LLC)層組成。PHY層有三個主要的模塊:發射器、接收器與Tx/Rx切換開關。這三個模塊皆以Simulink建模。MAC和LLC層則透過Stateflow圖表來建模,以顯示無線收發器MAC和LLC層的狀態變遷與邏輯運作。

發射器

在無線收發器的發射器模型,TxOn輸出控制了RF雙向切換開關來決定發射或接收,而TxSymbl輸出在發射時讓經過調變的訊號流出至雙向切換開關(圖4)。

輸入訊號TxDataOn和TxAckOn分別控制了資料架構和認可架構的發射期間長短。資料架構與認可架構分別載入至查找表TxData_LUT和TxAck_LUT。查找表變數的變更將改變被發射出去的內容。

發射器的符元速率(symbol rate)為10M symbols/sec,而位元速率(bit rate)為20 Mbit/sec。如果沒有符元要發射,或者節點處於接收模式時,TxSymbl會被設定為零。發射與接收的脈衝成形濾波器(pulse shaping filter)則在Tx/Rx Switch模塊裡面。

接收器

無線收發器的接收器有三個主要的功能模塊:訊號偵測(Signal Detection;SD)、決策回授等化器(Decision Feedback Equalizer;DFE)、解調器CRC(DCRC)(圖5)。SD模塊監控接收到訊號的功率等級。

一旦功率等級超出界限,SD模塊會產生一個訊號來啟動DFE與DCRC模塊,並開始將收到的訊號給DFE。DFE會以每個符元取樣兩次做為間隔。訓練參考前言被儲存在REF_LUT模塊。訓練資料會在等化訓練期間的一開始被呼叫出來。DCRC模塊負責將經過等化的符號流解調為一個位元流,辨認負載長度區塊的定界符號,以及執行表頭CRC來取得無錯誤的負載長度。

當負載長度被取得,模塊會執行負載(payload)的CRC操作,辨認收到的封包是資料架構還是認可架構,並且將架構類型資料提供給MAC層。如果任一個CRC失敗了,架構會被捨棄,且接收器會轉換回備用狀態。

訊號偵測器

圖6所示的訊號偵測器(signal detector;SD)被使用來偵測訊號何時抵達無線收發器。SD的波形呈現如圖7。訊號的絕對值會透過一個兩段指數移動平均濾波器(two-stage exponential moving average filter)來過濾。當移動平均濾波器的輸出超出界限,偵測器會產生啟動訊號SigDe來開啟DFE和DCRC模塊。位於輸出SigOut的緩衝模塊會產生二維(取樣)資料給部分的DFE。

決策回授等化器

無線收發器的DFE扮演了相當重要的角色。DFE的功能為移除符間干擾(intersymbol interference;ISI)、符元計時的同步、架構範圍的排列、頻率偏差的補償[1-2]。如圖8所示,DFE以符元速率來操作,並且在等化器權重的每一次疊代取兩個新的樣本。

由於前饋細胞(DFE_Cell_FFW)的輸入維度為2,每一個DFE_Cell_FFW模塊會執行兩個前向開關的過程。因此,在DFE的向前部分,9個Cell_FFW模塊被用來實現18個前向開關。在回授的部分,每一個DFE_Cell_FBW有一個一維輸入,並處理一個回饋開關。因此DFE有6個回饋開關。訓練的長度是在DFE內的N-Sample Switch模塊來設定。轉換器權重純量是在DFE內由「mu」命名的常數模塊設定。圖9為DFE前後的星座圖。

解調器CRC

DCRC模塊(圖10)將來自於DFE經過等化的符號流解調為位元流。它接下來檢查表頭架構CRC並解碼負載架構的長度。當取得負載架構的長度,DCRC內的Payload CRC模塊會啟動。當負載CRC通過,RxType Gen模塊會檢查MAC Header的To Address欄位。若To Address欄位符合節點的位址,模塊會依MAC Header的Type欄位產生RxDataOk或RxAckOk的訊號給MAC層。只要CRC失敗,或者是位址或資料類型不適當,則架構會被捨棄。

MAC層

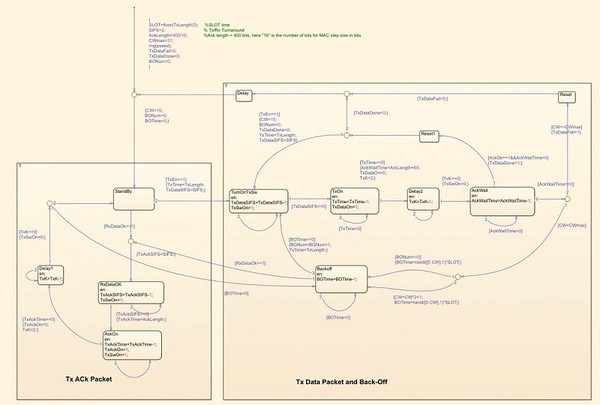

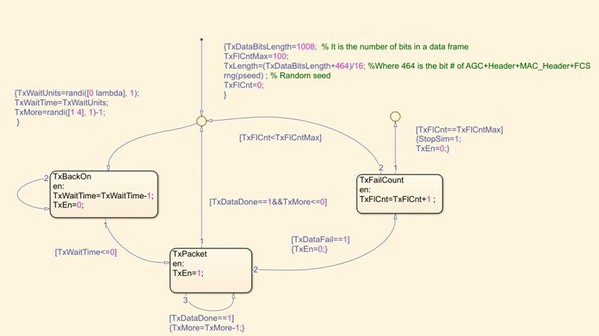

MAC對無線收發器執行有智慧的控制。MAC實現兩個可選擇的MAC功能:ALOHA-based(MAC_Sel=1)與CSMA/CA(MAC_Sel=0)。ALOHA-based MAC較為直接,而CSMA/CA MAC則更有效率。

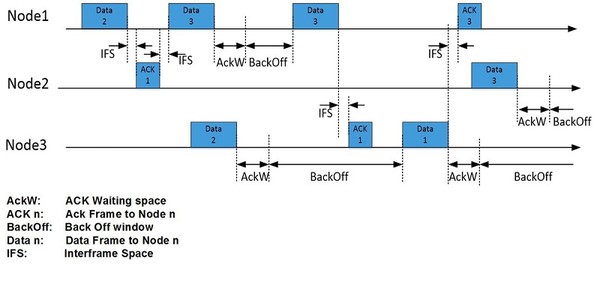

對於以ALOHA為基礎的MAC(圖11與12),當一個節點發射出一個資料架構時,它會期待在AckW定義的期間之內收到一個來自接收端節點的認可架構。如果在AckW內沒有接收到Ack,MAC會進入隨機的補償(back-off)程序。這一個補償程序會重複直到資料架構成功送出或者達到最大的重試次數。

| 圖11 : 在ALOHA-Based MAC的資料架構傳輸 |

|

| 圖12 : ALOHA-based MAC的Stateflow圖表 |

|

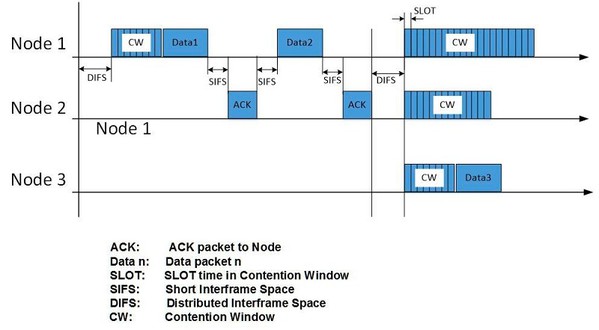

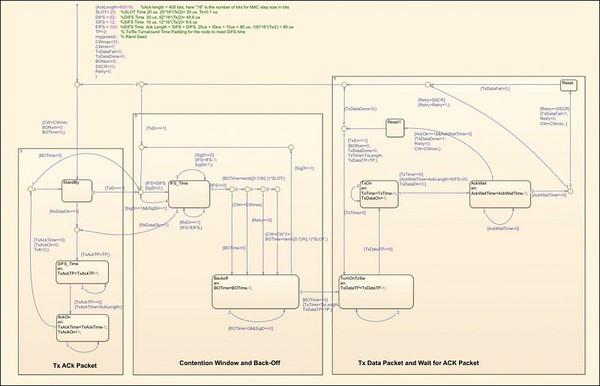

對於CSMA/CA MAC(圖13與14),媒介在DIFS發射之前這段期間必須靜止,接下來節點會開始隨機的競爭視窗(Contention Window;CW)期。當CW結束,如果媒介仍為靜止,節點會開始發射一個資料架構,否則,節點會等到另一個靜止的DIFS期。當發射的節點在SIFS期收到認可架構,它會發射出下一個資料架構;否則會再一次進入DIFS期間。

| 圖13 : 在CSMA/CA MAC的資料架構傳輸 |

|

| 圖14 : CSMA/CA MAC的Stateflow圖表 |

|

圖15為有兩種MAC功能可選擇的MAC層結構。

邏輯鏈路控制層

邏輯鏈路控制層(Logical Link Control Layer;LLC層)掌管較上層與無線收發器之間的隨機資料封包(圖16)。它產生隨機抵達的資料封包。對於一個很長的資料封包,LLC層會把它分割為幾個資料架構。LLC層也控制資料架構的排列,以及監控資料封包的傳送狀態。

| 圖16 : 邏輯鏈路控制層(Logical Link Control layer)的Stateflow圖表 |

|

結果與呈現

本文描述的Simulink模型有三個以輪替的方式溝通的無線收發器節點:節點1 →節點3→節點2→節點1。在每一個節點,由LLC層產生的資料封包抵達時間是隨機的。一個資料封包可能有多達四個資料架構。資料框負載長度設定為126 bytes。系統位元率為20 Mbit/Sec。通道模型是透過一個雙路徑瑞利通道模式(two-path Rayleigh channel mode)搭配50 Hz的都卜勒頻率擴展(Doppler frequency spreading)和25 dB SNR(Eb/No)的AWGN來建立。

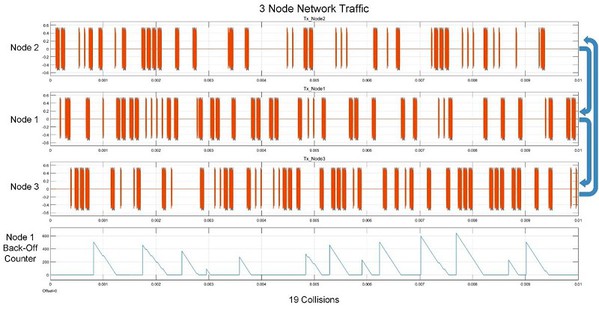

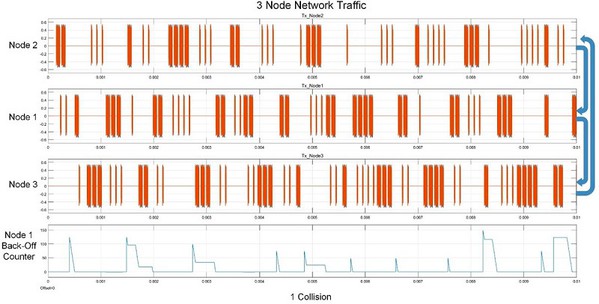

在ALOHA-based MAC(圖17),上面三個圖表為來自三個節點的發射波形,而底下的圖表為節點1的補償計數值。在這個圖表,持續時間較寬的訊號為資料框,而持續時間較窄的訊號為認可框。圖18描繪了CSMA/CA MAC相似的圖表。

從圖17與18呈現的結果,我們可以歸納出以下結論:

*任兩個節點之間,或三個節點之間都有可能發生衝突。

*成功的發射後面總是會有一個認可架構。

*短暫的周轉時間對於高網路通量相當重要。

*由於CSMA/CA MAC採用載波偵聽的關係,它比起ALOHA-based MAC更有效率。

| 圖17 : 有ALOHA MAC的節點波形。上:網路節點的發射器波形。下:節點1的補償計數值。 |

|

| 圖18 : CSMA/CA MAC的節點波形。上:網路節點的發射器波形。下:節點1的補償計數值。 |

|

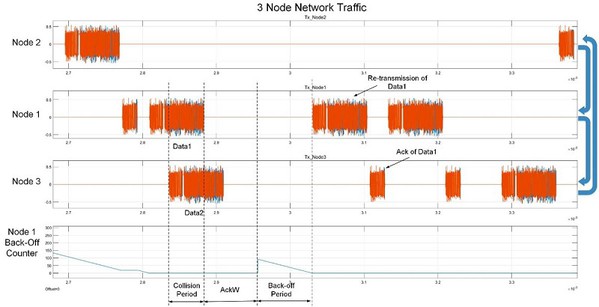

圖19為2.8 ms到3.4 ms這段期間媒介傳輸的放大圖。我們可以看到Data1與Data2這兩個資料架構發生衝突,因此節點2和節點3都沒有辦法產生認可架構。在AckW這段等待期間之後,節點1和節點3知道它們的資料框並沒有通過。接著在一段短暫的補償(back-off)時期之後,節點1重新送出Data1,這次資料框成功通過,並且接收到節點3傳回的認可。

| 圖19 : 圖17之2.8 ms至3.4 ms期間的放大圖 |

|

總結

在這個範例,我們建立了一個包含了多個無線收發器與衰減通道的無線網路的Simulink模型。這個模型是由Simulink模塊與Stateflow圖表所組成,展現了模型化基礎設計的效率。無線收發器有PHY和MAC層。PHY層模型提供了一般PHY的基本功能:調變、解調變、訊號偵測、同步、等化、位元操作(bitwise manipulation)、表頭CRC、架構CRC。MAC層模型是透過Stateflow來建立。它可以使用ALOHA-based MAC或CSMA/CA(IEEE 802.11)MAC。這個模型也有助於進行HDL實現與SDR原型化。

有了這個模型,我們可以在考慮了所有系統元件的網路環境下研究無線收發器的幾種行為,包含了:

*快速同步、等化、與轉向

*以架構為基礎與以樣本為基礎進行處理的比較

*PHY與MAC之間的互動

*具備幾種通道模型的網路效能

藉由使用通訊工具箱(Communications Toolbox)、事件模擬模塊組(SimEvents)附加的功能模塊,你可以將這個Simulink模型延伸運用到更先進的無線收發器上,如WLAN、V2X與無線IoT。

(本文由鈦思科技提供;作者Chung Wu任職於MathWorks公司)