二氧化鉿(HfO2)具鐵電相(ferroelectric phase)的這項新發現,已再次引起半導體界對鐵電材料記憶體的興趣。具非揮發性且以二氧化鉿為基礎的鐵電場效電晶體(ferroelectric field-effect transistor,FeFET)便是個例子,它展現了3D NAND記憶體類型儲存應用和記憶體內運算(in-memory computing)的特性。愛美科技術總監Jan Van Houdt將解釋FeFET運作機制,以及預測這項令人振奮的「新選手」會怎樣融入下一代記憶體的發展藍圖。

鐵電場效電晶體:具備記憶的電晶體

鐵電體(ferroelectrics)是一種材料,其晶體展現了自發電極化的現象。鐵電體可能處在二元狀態(二態),可透過外部電場逆轉。當施加外部電場時,鐵電材料晶體內形成的電偶極往往會自行平行於電場方向。當外部電場移除時,鐵電材料會保持在極化狀態,這也讓鐵電材料具備非揮發性。鐵電材料的極化電荷和外加電場有非線性的關係,也讓鐵電的極化-電壓(polarization-voltage,P-V)特性呈現遲滯迴路(hysteresis loop)的形態。

| 圖一 : 鐵電體(ferroelectrics)晶體展現了自發電極化的現象。鐵電體可能處在二元狀態(二態),可透過外部電場逆轉。 |

|

為了發展DRAM類型的記憶體應用,鐵電材料正在開發中—鐵電被用來當作DRAM電容器的介電質。但其實也可以把鐵電材料用來代替高介電常數金屬閘極電晶體(high-k/ metal-gate transistor)的閘極介電質,最終會製成一種非揮發性的電晶體,也就是鐵電場效電晶體(ferroelectric field-effect transistor),或稱FeFET。

現在運用鐵電材料製成的閘極絕緣體,其兩種穩定的殘餘極化狀態會改變電晶體的臨界電壓,即使移除供電電壓也是如此。因此,此二元狀態會被編寫在電晶體的臨界電壓中。要將資料寫入記憶體記憶單元,可以在電晶體的閘極施加脈衝,閘極會改變鐵電材料的極化狀態,並影響臨界電壓。

舉例來說,施加正脈衝會降低臨界電壓,並讓記憶單元的電路處在「開」的狀態。而讀取資料則是透過測量汲極電流。這種記憶體運作模式和NAND Flash的記憶單元類似,後者的電子被迫在浮閘(floating gate,FA)進出,以類似的方式影響浮閘電晶體的臨界電壓。

夢想成真

鐵電記憶體在超過五十年前被發掘,因為它的功耗需求極低、具備非揮發性且轉換(switch)速度快,一直被視為儲存應用的理想技術。然而,複雜鐵電材料的議題已帶來嚴峻的考驗。早期嘗試的材料是基於鈣鈦礦族的鋯鈦酸鉛(lead-zirconate-titanate,PZT),但要將這些材料保形沉積在電晶體上,已被證實是非常困難的。而且這些材料的介電電流極高(約300),這也阻礙了該材料和功能型電晶體的結合。

二氧化鉿(hafnium-oxide,HfO2)是著名的材料,且複雜性較低,近期被發現具鐵電相,讓發展這項記憶體技術的想法再次被觸發。研究者發現了斜方晶相(orthorhombic crystal phase),也就是鐵電相,可以透過將二氧化鉿摻雜到—像是矽(Si),使該相穩定。和鋯鈦酸鉛相比,二氧化鉿的介電電流較低,且能被保形沉積在薄層上。

此外,二氧化鉿也是已知被用來當作邏輯元件閘極堆疊的介電材料。只要巧妙地改變這個和CMOS相容的材料,邏輯電晶體就能轉變成非揮發性的FeFET記憶體電晶體。

接著…從平面走向垂直面

以二元、平面結構製成功能型FeFET已經證實可行。但二氧化鉿可以製成保形的階層,也就代表它也可能製成立體結構,像是將鐵電材料沉積在垂直面的「牆」上,然後在第三維度上堆疊電晶體。

就材料而言,3D FeFET可以解決2D FeFET結構帶來的一些挑戰。其中一項挑戰便是二氧化鉿介電質的多晶性質(poly-crystalline)。擴增二氧化鉿層的維度會大大限制每層的晶粒數。不同晶粒的極化方向並非全部相同,這會影響晶粒對外部電場的反應,導致高度變異性(variabilities)。藉由採用3D結構,這種限制至少能在第三維度上排除,因而削弱變異性,並讓數據更好控管。

垂直式FeFET技術和3D NAND類型的製程相容,後者一直是愛美科努力實現的方向。3D NAND Flash是當今主流的高密度資料儲存媒介,其價位相對便宜,且具非揮發性,但缺點是結構複雜,且運作速度慢。

和複雜的3D NAND Flash相比,這些垂直式FeFET預計會有幾個好處,包括更簡化的資料處理流程、更低的功耗以及更高的處理速度。相較於3D NAND Flash,垂直式FeFET可能以更低的電壓進行編程(大約4V,而NAND是20V),這也提升了可靠性和尺寸擴充性。

最初結果:2V記憶體窗、類似Flash的耐用性

愛美科從幾年前開始便一直專注於開發3D NAND類型的垂直式FeFET,因此,愛美科也運用他們發展進階3D NAND Flash技術的傑出經驗,並結合早期研究以鋯鈦酸鉛為基礎的鐵電材料記憶體時所用的工具、背景和載體。自2016年起,愛美科和合作夥伴們建立了產業合作計畫,共同研究垂直式FeFET。

在該計畫的架構下,研究團隊主要處理3D FeFET在資料處理、特性分析(characterization)和可靠性方面的挑戰。舉例來說,該團隊正在建立如何穩定二氧化鉿斜方晶相(即鐵電相)的技術訣竅。該相可透過像是矽在二氧化鉿層進行替代性摻雜(substitutional doping)來獲得。這樣能在該薄層產生應變(strain),讓晶體呈現預期的斜方晶相。

矽被視為較合適的摻雜原子是因為其熱積存(thermal budget),也就是說,它能保留鐵電相,但該團隊也在研究其它替代摻雜物,諸如鋁(Al)和鑭(La),同時研究鉿鋯基氧化物(hafnium-zirconium-oxide),以作為替代的鐵電材料。

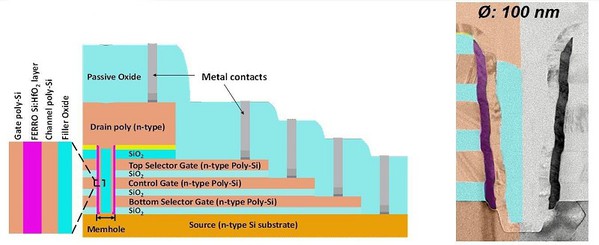

愛美科近期展示了首個功能型垂直式二氧化鉿FeFET,其結構為通心麵形狀的3D NAND。該元件根據愛美科處理3D NAND Flash的流程來製造,目前還取代了傳統的ONO介電層(oxide-nitride-oxide),改採用8nm且摻雜矽的二氧化鉿層,以原子層沉積法沉積(atomic layer deposition,ALD)。多晶矽被用來當作閘極材料,而非晶矽則是通道。

該測試載具(test vehicle,TV)包含了一垂直弦,讓三個閘極(控制閘極、底部和頂部選擇器閘極)串聯。該弦內部的孔洞先以氧化物填滿,再掘入內凹(recess),因此結構看似通心麵。在真實的3D NAND類型元件中,在垂直方向上的控制閘極數量可多達64個,以實現高密度記憶體解決方案。

| 圖三 : 圖左為通心麵型的3D FeFET切面示意圖,可見三個記憶單元串聯;圖右為穿透式電子顯微鏡(transmission electron microscopy,TEM)下的切面圖(直徑:100nm)。 |

|

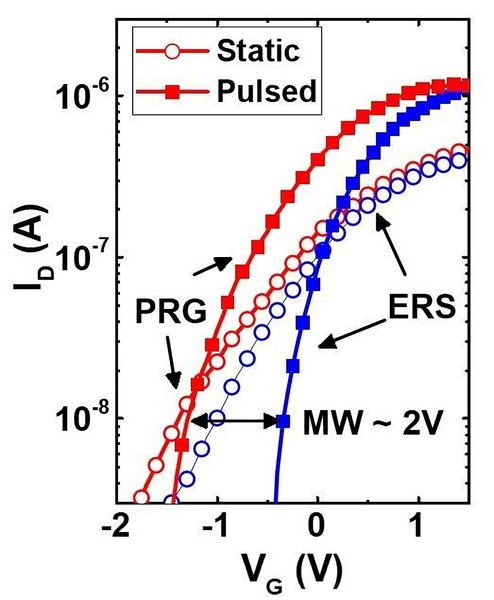

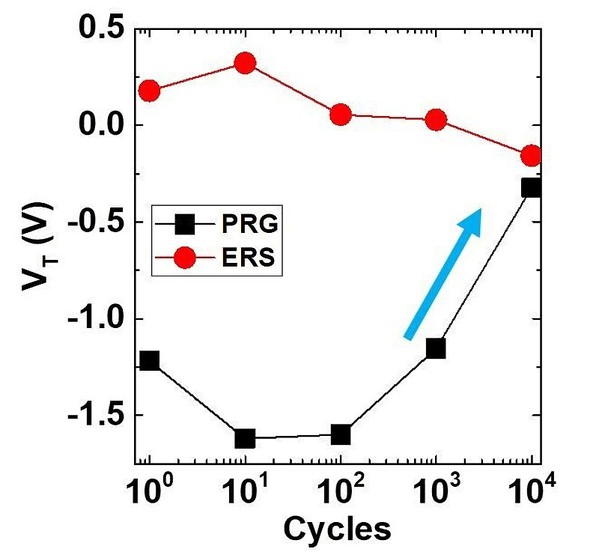

就此測試載具來說,在施加100ns的寫入/擦除脈衝後,可獲得將近2V的記憶體窗。FeFET也展現了85℃的資料儲存能力(retention):在攝氏85度下運行100小時,二元狀態的區分還是很明顯。該研究團隊也表示FeFET的耐用性高達10的4次方,和Flash相似,且已完成首次可靠性測試。由施加在介面的高電場造成的電荷捕捉現象限制了FeFET的重複擦寫能力(cycling performance),這點也被提出來討論。減少介面層的厚度可能可以處理這個問題。

| 圖四 : 記憶體特性分析:至多高達2V的記憶體窗能在施加100ns寫入/擦除(PRG/ERS)脈衝後獲得。 |

|

| 圖五 : 可靠性特性分析:臨界電壓(threshold voltage,VT)和循環次數在寫入和擦除後的發展。記憶體窗的結束發生在10的4次方的次循環之後。 |

|

3D NAND類型的應用及機器學習

FeFET還處在研發的早期階段,要斷言量產可不可行或何時達成都還言之過早。但這項富前瞻性的新記憶體概念已引起產業要角濃厚興趣。而愛美科的角色便是探索FeFET的最大潛能,並讓合作夥伴在該研究領域能領先起步,進而讓他們做出決策要如何讓FeFET最佳化地融入其產品和晶片。

FeFET作為一種可獨立運行的記憶體,據信將成為儲存級記憶體(storage class memories,SCMs)的一員,就字面上來說,也代表它將弭平DRAM和NAND Flash的界線,前者速度快且具揮發性,後者速度慢、具非揮發性且密度高。FeFET是非揮發的,相較於NAND Flash,它還有幾個優點:FeFET轉換速度較快、資料處理更簡易、功耗較低,且有潛力能以更低壓運作。然而,雖然就速度而言,FeFET更接近DRAM,但FeFET的重複擦寫能力(為10的4次方,而DRAM為10的12次方)有限,這很可能會讓它在DRAM和NAND這條分界上更傾向NAND那方。

FeFET記憶體在邏輯元件代工廠領域也引起注意,因為FeFET的高速特性很可能有利於機器學習應用—此應用需依靠記憶體內運算(in-memory computing)來達成。因此,目前有好幾種記憶體在探索該應用,包括Flash、磁阻式隨機存取記憶體(magnetic RAM,MRAM)、電阻式隨機存取記憶體(resistive RAM,RRAM)、相變記憶體(phase change memory,PCM)、靜態隨機存取記憶體(static RAM,SRAM)和FeFET。因為FeFET的非線性特性和速度,它成為額外引人注目的技術,用來開發以深度學習卷積神經網路運轉的機器學習應用。就這類應用,平面式的FeFET很可能會先出現。

展望:邁向更高密度FeFET之路

NAND Flash技術的其中一項特別優勢是:其記憶單元的容量最高為4位元,這也使得該技術擁有獨一無二的高資料密度。在傳統的單階記憶單元(single-level cell,SLC)中,每個記憶單元能處於二元狀態中的其中一種,且每記憶單元儲存1位元的資料。工業型NAND Flash已從單階記憶單元進化,每記憶單元已可儲存2位元、3位元甚至4位元的資料。每單元儲存4位元的記憶體需在每個電晶體中編設16個臨界電壓狀態,使得所需記憶體窗變得龐大。

但就FeFET而言,愛美科認為有三種方式能提升其資料密度,並使之成為能與NAND Flash競爭密度的強勁對手。首先,如果臨界電壓能維持充分穩定狀態,FeFET的2~2.5V記憶體窗原則上能達成每記憶單元2位元的編程,也就是說,每個電晶體需配置4個臨界電壓狀態。

第二,透過採用類溝槽(trench-like)的結構來連結電晶體,每記憶單元的資料密度就可以翻倍,溝槽的兩邊各配置兩顆電晶體。在現今的3D FeFET設計中,像是愛美科的通心麵型NAND結構,控制閘極是以環繞式閘極結構(gate-all-around structure,GAA structure)來設計。這表示閘極被通道包圍,限制了電晶體數量,每層和每弦僅一顆。環繞式閘極結構在NAND Flash是必需的,是因為要用來改善浮閘或氮化矽捕陷層的電荷注入,但FeFET並無此需求。

愛美科目前正在探索能替代類溝槽結構的選項,以實現在溝槽側壁上堆疊電晶體,而現在的電晶體分別放在溝槽的頭尾。此新型架構應該會讓記憶單元的密度高出一倍,還會降低記憶單元間的變異性。

第三,FeFET記憶體單元可能會微縮至更小的尺寸。在傳統的NAND Flash記憶單元內,ONO介電層的厚度約為20nm。但在FeFET記憶單元中,二氧化鉿鐵電層預估能微縮至4nm。此外,在垂直方向上,因為FeFET的工作電壓比NAND Flash還低,FeFET的字元線距會比較短。

總而言之,3D FeFET擁有多條邁向高密度的發展之路,同時也會朝向高速、非揮發、類似Flash的耐用性、低工作電壓和低功耗這些面向發展,這些潛能在在使得3D FeFET成為對戰3D NAND類型應用的強勁選手。

(本文由愛美科授權刊登,作者Jan Van Houdt為愛美科半導體科技與系統部技術總監;編譯/吳雅婷)