可程式設計斜坡產生器(PRG)(在Microchip的幾款8位元PIC微控制器上提供)是一種高度靈活的類比周邊,旨在簡化需要電壓線性變化的應用。顧名思義,PRG能夠以軟體的方式控制其輸出產生上升、下降或交替的上升/下降斜坡。經過簡易的設定後,周邊能夠獨立於核心外自主運行外,進而釋放中央處理單元(CPU)的效能來執行其他任務,進入低功耗模式或以其它方式在系統中承擔更多監督角色。

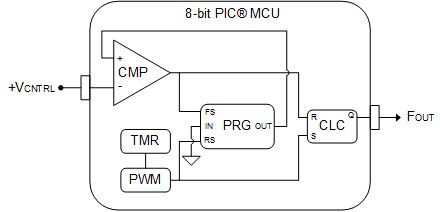

透過控制整合的恆流源可以動態調整上升和下降時間。憑藉靈活的輸入和輸出選項,設計人員可以自由地與晶片外訊號源或微控制器上其他周邊的訊號互連。這通常會使系統回應更快,同時可通過減少外部元件數量來盡可能減少潛在的噪音源及縮小應用尺寸。圖一顯示周邊的框圖。

用於配置 PRG 的有用工具是 MPLAB 程式產生器(MCC),這是一個簡單易用的 MPLAB X整合式開發環境(IDE)外掛程式,見圖二。它可產生用於控制和驅動 Microchip PIC 微控制器周邊(如PRG)的驅動程式。PRG 可以實現不同的功能,每個功能都可以使用 MCC 進行設置。

三角波產生器

三角波產生器(TWG)產生週期性的非正弦波形,其三角形形狀具有相等的上升和下降時間。要產生三角波,PRG必須配置為交替上升和下降模式。MCC允許配置上升(RS)和下降(FS)時脈輸入源。PRG使用這兩個觸發斜坡上升和下降的參考電壓來確定輸出振盪頻率。這兩個參考電壓還可確定三角波訊號的最小和最大電壓值。

當 PRG 輸出低於數位類比轉換器(DAC)設置的電壓大小時,PRG 的 RS輸入被觸發,內部電容充電。當 PRG 輸出超過固定參考電壓(FVR)時,FS 輸入被觸發,內部電容放電。

由於PRG無法指定的其輸出接腳,因此PRG的輸出需透過一個可配置的運算放大器進行緩衝後輸出。可以計算輸出頻率,但其精確度可能受到不同因素影響,例如電容的寄生電阻、雜訊、生產差異和溫度。

頻率值隨著DAC輸出電平或PRG斜率(SR)的改變而變化。輸出斜坡的SR通過PRG的當前設置進行配置。

圖四提供了實際建置的理想行為。通常,產生的三角波由對稱的週期性交替上升和下降斜坡組成。

最大電壓和最小電壓分別由VFVR和VDAC定義。當訊號達到最大電壓或最小電壓時,將設置上升觸發和下降觸發。在MCC中更改斜率設置可用於調整頻率。VDAC的變化也會導致頻率變化,但最小電壓會相應地增加或減少。

PRG的振盪頻率取決於所選的汲入電流和輸出電流、內部電容以及設置的上升觸發和下降觸發。通過在PRG的輸出上放置額外的電容,可以實現更低的頻率範圍。

通過添加可配置邏輯單元(CLC)和外部電容C1,DAC和FVR設置的電壓閘變點可分別觸發上升事件和下降事件。在運算放大器的輸出端添加C1,使其與PRG的內部電容有效並聯。額外的電容延遲了觸發事件之間的時間,從而產生較低的FOUT頻率。

在比較器的輸出端連接CLC,使波形產生器產生方波和脈衝。CLC配置為SR鎖存器,低頻FOUT來自其輸出。與PRG類似,參考電壓觸發置位元和重定輸入。FOUT在C1的電壓(OPAOUT)低於DAC電壓大小時置位元。一旦OPAOUT高於FVR,就會清除FOUT。

電壓控制振盪器

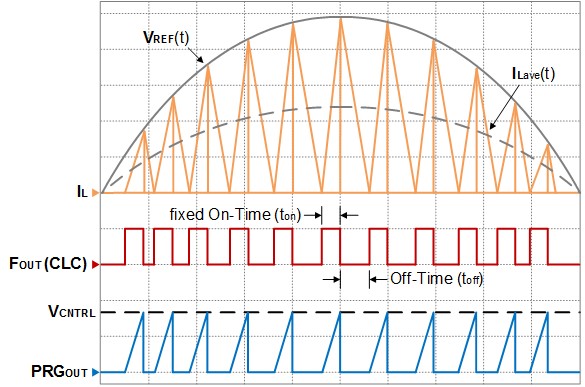

電壓控制振盪器(VCO)是一種輸入控制電壓決定其振盪頻率的電子振盪器。VCO的暫態頻率通常設計成與暫態電壓成線性比例;輸入電壓越高,其振盪頻率也越高。VCO實現的PRG操作與TWG類似,不同之處在於輸出頻率來自CLC的斜率鎖存器,可變電壓VCNTRL設置PRG的RS輸入。

如果VCNTRL的輸入升高,則會縮短重新觸發上升事件所需的時間。因此,汲入電流和輸出電流之間的切換變得更快並且振盪頻率增加。

圖七給出了控制電壓與輸出頻率之間的關係,其中有三個PRG斜率值。可以針對期望的頻率範圍改變SR值。較低的SR值可以產生從幾Hz至大約500 kHz的頻率。但較大的SR值可以達到兆赫茲範圍。

根據兩個控制電壓值和一個恒定斜率,VCNTRL降低時,CLC的VCO頻率輸出也會降低。

電壓控制工作週期振盪器

標準VCO電路直接修改振盪器頻率。此外,對於電壓控制工作週期振盪器(Voltage-controlled duty cycle oscillator, VCDCO),其控制電壓則會修改其輸出脈衝的工作週期。

除了時基觸發輸出脈衝發生之外,對VCDCO也實現了類似的VCO設置。PWM 和 TMR 模組決定振盪器的週期和頻率,而 PRG 通過 VCNTRL 確定其工作週期。

| 圖八 : 使用基於時間的觸發來實現電壓控制的工作週期 |

|

PWM的上升沿觸發 PRG RS 輸入並使 CLC 輸出置 1。當 PRG 輸出超過VCNTRL 時,FS 輸入被觸發,PRG 電容短路並且 CLC 復位。PRG 和 CLC輸出將保持低電平,直至下一個 TMR 溢出和 PWM 正緣。

增加 VCNTRL 會延長斜坡的上升時間和輸出的正脈衝寬度。

工作週期計算為VCNTRL與VMAX的比值。為了提高工作週期的範圍,當控制電壓達到給定斜率的VMAX時,計時器週期應等於斜坡的上升時間。

當使用兩個不同的VCNTRL值時,由於計時器和PWM的週期恒定,因此RS觸發序列在兩種條件下統一。但是,由於斜率恒定且VCNTRL較高,在FS觸發之前可能會有一個額外的延時。

PRG斜率和TMR2週期值取決於VCDCO所需的頻率和工作週期範圍。PWM的工作週期可以設置得足夠低,以觸發PRG的RS輸入。FOUT仍然來自CLC SR鎖存器。PWM和CMP輸出還為CLC提供置位(S)和復位(R)的輸入。

非同步單觸發

非同步單觸發(AOS)在外部觸發時產生單輸出脈衝。AOS通常稱為單穩態多振源,基本上是處於一個穩定狀態。如果其穩定狀態為低電平狀態,則外部觸發訊號會將輸出驅動為高電平並持續一段時間。在一個週期結束時,AOS返回其穩定狀態並等待下一個觸發事件。

CLC的重置模式是AOS的穩定狀態。外部觸發會將PRG的RS輸入置位,並獨立於CLC將AOS的輸出置位。當PRG達到FVR時,FS輸入源被觸發,PRG中的內部電容短路,CLC輸出復位。脈衝寬度的持續時間取決於FVR電壓和PRG斜率。

外部電壓觸發可以取代PWM和TMR模組來消除PRG RS輸入和和CLC置位源的週期性觸發順序。輸出脈衝則是來自於CLC輸出。

電壓控制單觸發

接下來的這個例子是前一次單觸發的升級版。使用一個輸入做為觸發訊號,而另一個輸入則做為單觸發的週期。單觸發的一個應用控制臨界導通模式(CrCM)PFC控制器的導通時間。

輸入電壓VCNTRL確定輸出的單觸發週期或導通時間。VCNTRL的值越大,導通時間越長。當PRG的上升斜坡訊號達到VCNTRL時,PRG電容短路,互補輸出產生器(COG)工作週期完成。輸出保持低電平,直至訊號重新觸發PRG上升斜坡及COG週期開始。

在臨界導通控制器中,COG控制功率金屬氧化物半導體場效應電晶體(MOSFET)的開關。來自誤差放大器的回饋訊號被饋送到VCNTRL。恒定的回饋訊號將導致固定的導通時間。在導通和關斷狀態期間,電感電流斜升至輸入參考電壓對應的值並分別回落到零。圖11給出了CrCM控制器的電感電流的典型特性。

| 圖十一 : 固定導通時間CrCM控制器的電感電流波形 |

|

要使用MCC配置周邊,請使用第二個CMP替換PWM和TMR模組。在正負輸入源列表中,分別選擇CINx+ 接腳和FVR。選擇COG模組來代替CLC並將比較器設置為上升和下降的事件源。對於功率轉換器應用,COG周邊更適合作為輸出驅動器。

結論

憑藉PRG的豐富功能,可輕鬆地產生電壓斜坡作為參考訊號或時脈源,並使用親切易懂的MCC來輕鬆配置這些功能。與Microchip PIC微控制器中的其他幾個周邊配合使用時,可以探索更多基於PRG的應用。

(本文作者Mary Iva Rosario Salimbao為Microchip Technology應用工程師)