首先,舉一個實際的IC規格為例,並考量精準度會產生什麼效應。這裡所採用的是一顆高階FPGA。FPGA的參數決定了IC保證運作下電源供應器的電壓。若電源供應器超出這個範圍,就無法保證元件能運行。

接著來看VCC rail,在額定的0.85伏左右,其具有正負30毫伏的變動。對於0.85伏特的電源軌而言,其誤差值為正負3.5%。

乍看之下,會認為正負3%的負載點(Point of Load, POL)就能應付這個狀況。但不幸的是,還必須考慮其他的因素。

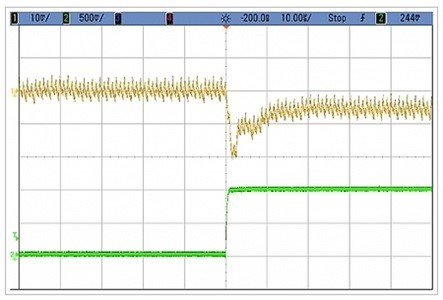

| 圖一 : 10安培POL負載響應(Load Response) |

|

圖一的示波器截圖顯示了在VCC POL輸出端上,一個10安培的負載脈衝。另外還有約8毫伏的漣波,以及20毫伏的短暫電壓降(short drop)。這讓人質疑這些瑕疵訊號(artifacts)是否必須是維持在正負3.3%的規格範圍內?示波器截圖的波形是POL的輸出端。要問的是,負載看到什麼?

這是一個電源分配網路(PDN)電路圖,圖中顯示封裝與晶片內的濾波電路。PDN、封裝解耦合、以及晶片內電容,都會過濾掉一些瞬變的高頻率部分的雜訊。

因此,對於瞬變的餘裕規劃問題,答案是,需視情況而定。一般而言,只有PDN封裝尾端的部分,會濾掉最高頻率的瞬變。

漣波是另一個重點。漣波的頻率較低,不論在負載針腳上看到什麼樣的漣波,都會在晶片上看到同樣的漣波。因此,對於進行分析的目的而言,會假設漣波會消耗掉一部分的誤差餘裕,並忽略瞬變。

由於本範例的漣波為8毫伏,所以誤差預算僅有正負2毫伏,或精準度約正負2.5%。不幸的是,這還沒結束。還得考慮過壓(OV)與欠壓(UV)的監控器。OV/UV監控器的功能,等同於比較器及設定跳脫點(trip points)的DAC元件兩者的組合。因此關注的重點,在於欠壓與過壓的精準度。

監控器的精準度是誤差預算的一部分,這是因為希望把UV監控器的精準度設定高於規格的要求,OV監控器的精準度則希望要低於規格。也只有這個方法能保證電源軌符合IC的電源供應規格(註:通常可在監控器加入一些濾波元件,以防止各種瞬變(transient)讓監控器跳脫,並確保一旦出現漣波就會讓監控器跳脫。)

這裡是採用LTC3880監控器的正負2%精準度來做為例子。在0.85伏的電源軌上輸送17毫伏的電力,此時預算只剩下4毫伏,POL輸出電壓的精準度必須為0.5%,能辦到嗎?

LTC3880規格表顯示輸出精準度在伺服端(server)導通時為正負0.5%。這可以得到一個符合規格的電源軌,還有監控器可提供確保一旦不符合規格時,可以利用監控器執行跳脫或關閉,然後傳送一個故障訊號到母板管理控制器(BMC)。

整理一下目前實施的數據:FPGA 規格: 30毫伏;移除漣波: 22毫伏;移除監控器精準度: 4毫伏;移除控制迴路精準度: 0毫伏。這能折衷嗎?

這個問題就要視預期的品質等級。如果把監控器移出規格外,僅依賴控制迴路,那麼控制迴路要求的精準度則是2%,相較之下,LTC3880就優於其4倍。意謂它能支援低於0.85伏的電源軌。但是現在仍還沒有考慮最後一個層面,後面還有更多。

該如何規劃裕量(margining)?

在生產環境中,電源供應系統會在正常規格下運作,或是在超出與低於規格的狀態下運行,排除系統中任何罕見狀況(marginalities)。在此設計案例中,意謂在正負3.5%規範下運作系統。在規劃裕量時,監控器會預留一些餘裕度,因為目標是要確保系統在整個規格範圍內維持可靠運作。

由於必須保證在極端狀況下依然正常運作,因此必須將電源軌設定在即使超出極端狀況下,也能夠運作,並且能藉由控制迴路的精準度,確保實際數據達到甚至超過極端值。如果控制迴路的精準度為0.5%,就必須將電源軌設定為±4%。但要是只有一個精準度為2%的控制迴路,接近控制器的水準,那該如何因應呢? 數值應該是±5.5%。

如果FPGA規格因為較高的餘裕數據而失去時序調節的餘裕空間,餘裕測試可能會開始出現代價不貲的失敗。因此,必須在設計中增加時序餘裕度以通過餘裕測試,如果不能容許這樣做,可能就得承擔損失良率的後果。或者,可以藉由允許逸出(escapes)來調降餘裕值與品質,但兩者都會讓自己或客戶蒙受損失。

如果採取正確作法以及設定正確的餘裕值,那麼專案則會延遲,同時會面臨良率下滑以及損失收益的情況。但如果在餘裕測試上作手腳,受害的則會是你的客戶,因為對他們而言,系統會變得不穩定。所以,控制迴路的精準度扮演非常關鍵的重要性,它的影響至深且遠。

請詳閱元件規格

請千萬要詳讀製造商提供的規格資料。每家製造商在規範精準度方面都使用自己的架構。控制迴路的精準度是由多個元素構成的:

1.電壓差放大器偏置(offset)與增益(gain);

2.ADC的參考電壓(Voltage Reference);

3.ADC的偏置與增益

4.電阻分壓器(resistor dividers)這類外部元件的貢獻

有時資料表會分別規範這些數據,或在規格書中缺漏部分資料,甚至沒有直接規範輸出精準度。在比較各款元件時,若資料表沒有列出,就一定要計算總誤差。如果在後面的設計流程遇到問題,甚至到了量產才發現問題,就要後悔自己做出的選擇了。

總結

在審視FPGA規格並擬定誤差預算時,可以發現,誤差預算還包含著其他的元素,如漣波、控制迴路的精準度、監控器的精準度、以及餘裕精準度等。光是直接比較FPGA規格,以及POL的規格是無法一窺全貌。POL必須遠比FPGA資料表的數據還要精準,才能保證可在規格範圍內運作,以及確保在規格範圍內維持可靠運行,同時,在量產時能維持高良率。

(本文作者Michael Jones任職於Analog Devices, Inc.)