先進節點的邏輯和記憶體裝置要求化學機械平坦化/研磨 (CMP) 製程具有極高的性能。鑒於非金屬 CMP 製程數量的快速增加和不斷多樣化,此類節點對該製程提出了新的要求,如更高的平坦化效率、接近零缺陷率以及製程成本的大大降低。為達到技術和經濟的雙重目標,需要高度可調節、可稀釋的CMP 研磨液以及相匹配的 CMP 研磨墊和研磨工藝。在先進的前段製程中將有不同材料層的組合(如氧化物、氮化物和多晶矽),各材料都需要研磨,各層分別要求不同的研磨率、選擇比和嚴格的製程控制。

這些新的多樣化需求需要新的研磨液配方。一組新的介電層 CMP 研磨液將接受檢測,該研磨液使用先進的凝膠狀二氧化矽磨料和先進添加劑來實現高研磨率、高平坦化效率和低缺陷率。這個新近已商品化的研磨液以濃縮液形式提供給客戶,以將總體擁有成本降至最低。使用端稀釋可將磨料濃度降至最低,而不會影響 CMP 性能和工藝穩定性。

CMP 技術的趨勢和挑戰

隨著邏輯晶片和記憶體晶片廣泛應用於行動、伺服器、資料處理、通訊、消費電子產品、工業和汽車等領域,半導體行業對邏輯晶片和記憶體晶片的需求持續增長。透過技術節點的進展和降低成本來延伸摩爾定律,這一模式始終推動著對新電晶體/裝置架構與技術(包括 3D FinFET、3D NAND 和 3D 封裝)需求的增長。CMP 正是提供這些技術的重要基礎。

先進的邏輯節點所包含的 CMP 層數不斷增加(例如,由 45nm 12 層增加至 7nm 22 28層)。新的技術和材料不僅提供了新的機會,同時為 CMP 耗材和工具帶來新的挑戰。

除降低缺陷率和擁有成本外,必須對平坦化效率、Erosion和Dishing等主要性能因素進行嚴格的程式控制,以達到晶粒內和晶圓內均勻度要求。這些新的需求必須透過創新來滿足。

在先進的邏輯工藝中,POP 要求研磨氮化物和氧化物,停在多晶矽層。1 為減少柵格高度變化和Dishing,需要可調式研磨液和穩定的研磨墊壽命。SAC 工藝要求研磨氮化物,保留氧化物;這就要求使用高選擇性研磨液(氮化物:氧化物選擇性 > 50:1)。要達成無氮化物殘留表面,則可能需要多個細研磨工序,這使得可調整研磨液能成為一個很好的選擇。多晶矽柵 CMP 研磨非晶矽或多晶矽並研磨至同一層,晶圓內的柵格高度變化變得很重要。透過終點測量來管理最終厚度要求變得非常具有挑戰性;這要求研磨墊/研磨液工藝最好具有高平坦化效率,並有一定自動停止功能,從而控制柵格高度並降低表面粗糙度。

在淺溝槽絕緣層(STI)的製程下中,由於針狀結構翼變薄、變長,研磨液需具有極高選擇性(>100:1 Ox:SiN),以將氮化矽損失降至最低。用於填充縫隙(如在淺溝槽絕緣層工藝中)的新型可流動 CVD 膜對沉積和回火硬化製程較敏感,可能導致高缺陷率(微粒)和研磨率不穩定。

先進記憶體應用也增加了 CMP 工序(例如,在蝕刻工序後,細研磨製程可加在以使用硬研磨墊來降低缺陷率、提高整體均勻度的單盤(one platen)工藝中)。進一步縮小現有 DRAM 記憶體單元存在巨大的技術難度。DRAM 工藝需要不斷對CMP製程要求提高研磨率,從而提高產量、降低總體擁有成本。

先進節點的一個共同點在於,不管邏輯和記憶體(主要是 3D-NAND)都需要更多的 CMP 製程。 多種應用都需要具有特定可調整的研磨率、並能夠降低缺陷率和擁有成本的研磨液。

新研磨液配方

半導體製造商依賴與材料供應商密切合作,來發開發能滿足更嚴苛新需求的研磨液。例如,陶氏電子材料事業部近期開發出針對 ?20nm DRAM 應用和 ?28nm 邏輯應用的研磨液,實現了高氧化物研磨率、低缺陷率和低擁有成本。對於?14nm 的邏輯應用,不同的工藝要求需要氧化物研磨液具有高平坦化效率,低梯度,以及良好的多晶矽和氮化物的研磨率。

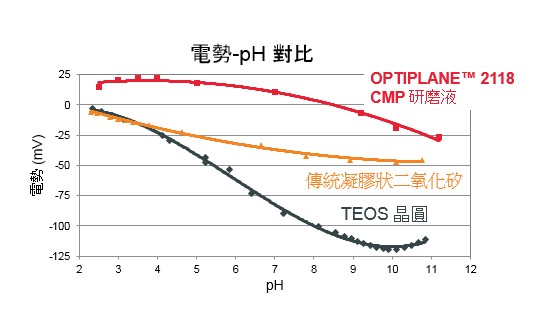

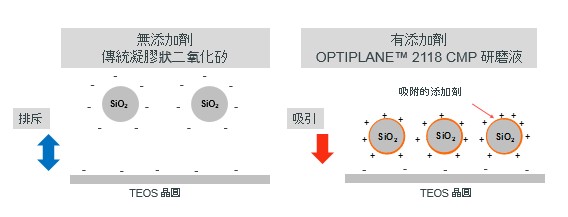

陶氏 OPTIPLANE 2118 研磨液是根據以上需求開發的一款研磨液產品。該產品為低磨料的酸性二氧化矽研磨液,用於平坦化先進 CMP 節點中的介電膜。此款研磨液的 CMP 效率提高,主要源於其獨特的配方可促進有利微粒/晶圓的相互作用。如電勢-pH 對比圖(圖一)所示,凝膠狀二氧化矽磨料表面帶負電荷,與已研磨 TEOS 膜的表面相同(根據 pH 2 至 pH 11 的所有測得 pH 範圍得出),因此在研磨中出現不利的靜電排斥。新研磨液配方中加入了專有添加劑,其等電位點的位置大幅移動,而且由於添加劑吸附於二氧化矽微粒表面,生成了帶正電荷的酸性 pH 表面。在此情況下,微粒自動吸附於晶圓表面,大大減少了使用端磨料用量,而不影響研磨性能(圖 二)。此優化配方精確控制微粒與晶圓的介面,從而將 CMP 的優勢發揮到最大。

| 圖一 : OPTIPLANE 2118 CMP 研磨液、傳統凝膠狀二氧化矽研磨液、TEOS 晶圓電勢-pH 對比 |

|

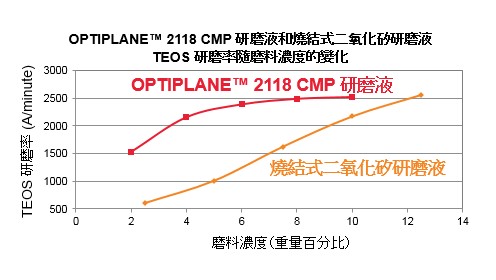

此研磨液由球形凝膠狀二氧化矽微粒和專有添加劑組成,添加劑吸附於磨料微粒上,將負電荷轉化為正電荷,如圖二所示。磨料微粒 (+ve) 和介電膜 (-ve) 間的最終靜電吸附力使研磨性能(材料研磨率/研磨負載)提高,如圖三所示。市場上的鹼性凝膠狀二氧化矽和燒結式二氧化矽研磨液很難在較低研磨負載下實現較高介電質研磨率,因此,此類研磨液通常作為磨料含量重量百分比 >12% 的層間介電層研磨液。與此相對,此新款研磨液配方的磨料含量重量百分比為 6%,可作為層間介電層研磨液用於使用端。

| 圖二 : 二氧化矽磨料-晶圓相互作用 (a) 無改變電荷的添加劑 (b) 有改變電荷的添加劑 |

|

| 圖三 : OPTIPLANE 2118 和燒結式二氧化矽研磨液TEOS 研磨率隨二氧化矽磨料負載變化 |

|

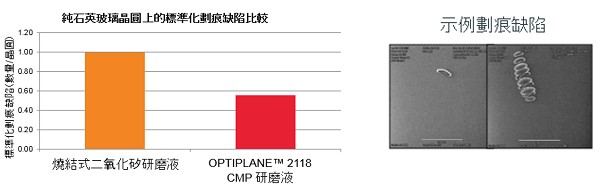

氧化物 CMP 過程中會產生各種缺陷,包括刮傷、微粒殘留、研磨墊碎屑和與粗糙度相關的不可見缺陷。一般認為,刮傷最影響晶圓產量。刮傷的形成通常是研磨液中大微粒數量增加的結果。

OPTIPLANE 2118 配方中含有高度可控的球形二氧化矽微粒, 並以先進的過濾技術製造。 此研磨液用於研磨純石英玻璃晶圓時,可減少約 45% 的刮傷(圖四),用於內部 TEOS 晶圓時, 相比類似研磨工藝下傳統燒結式二氧化矽,此研磨液可減少 > 70%的刮傷。此原因在於在使用端使用較低磨料含量,同時添加劑吸附於已研磨表面可產生位阻保護將可以將缺陷大大減少,並且大幅降低研磨溫度與研磨墊磨損。

| 圖四 : USG 晶圓上的標準化刮傷缺陷比較及刮傷缺陷示例 |

|

此新款商用研磨液配方可用於層間介電層研磨液,而我們的研發團隊正在開發針對先進的前段 CMP 工序(如 POP、SAC 等)的特定選擇性研磨液。借助內部開發工作以及與客戶的密切合作,OPTIPLANE 4000 產品系列還將推出支援各種研磨率和選擇性的其他商用配方。

結論

為滿足先進設備製造商對新的附加 CMP 工序的需求,新型研磨液配方可確保 CMP 工藝穩定,提高平坦化效率,大幅降低缺陷率。透過降低使用端磨料濃度,提高研磨率和消耗品生命週期,在提供先進性能的同時降低了工藝成本。CMP 研磨液創新助力下一代先進技術節點的成功,推動行業持續發展。

(本文作者Adam Manzonie (1)、Todd Buley (2)、Jia-Ni Chu (3)、Mike Kulus(4)為陶氏化學公司CMP 技術部1全球研磨液業務總監、2全球研磨液應用總監、3研磨液行銷經理、4戰略行銷總監)

致謝

作者感謝 Yi Guo、John Nguyen、Arun Reddy、Peter van der Velden 和 Matt VanHanehem 對此文章作出的貢獻。此外,還要感謝 Julia Chou 和 Linus Khoo 提供工藝要求,感謝位於德拉瓦州紐華克和臺灣新竹的應用實驗室團隊提供的技術支援。

參考資料

[1] Babu, S. (2016). Advances in chemical mechanical planarization (CMP), 1st Edition. Woodhead Publishing.

[2] Choi, J., Prasad, Y. N., Kim, I., Kim, I., Kim, W., Busnaina, A. A., & Park, J. (2010). Analysis of Scratches Formed on Oxide Surface during Chemical Mechanical Planarization. Journal of The Electrochemical Society J. Electrochem. Soc., 157(2). doi:10.1149/1.3265474.