在各種應用及領域中,有非常多的機會去使用到線性回授移位暫存器(Linear Feedback Shift Registers, LFSR) 。例如近似的隨機亂數序列PRBS (Pseudo Random Bit Sequence)、CRC (Cyclic Redundancy Check)的計算?最長序列(MLS)的產生,另外還有擾頻器(Scrambler) /解擾器(Descrambler)等等。

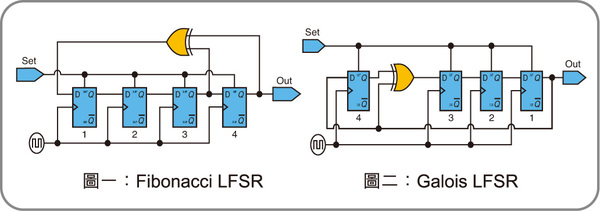

LFSR主要實作分為二種架構,因抽頭回授的位元而有所不同,分別為Fibonacci (圖一)及Galois (圖二)。一般使用上,或許會認為使用軟體(Software)的方式來實現即可。這是非常普遍的作法,並不需要大費周張去尋求特別的實現方法,但是卻忽略掉使用軟體方式來實現時,有可能因為中斷 (INT)的發生? 程式碼的分岐(Branch, Jump) 而造成LFSR輸出信號的不穩定、以及發生跳動(Jitter)的現象。

| 圖一 : Fibonacci LFSR Galois LFSR |

|

同時也因為是由軟體來控制LFSR , 所以也不能減少CPU的負載,也因為軟體 程式必須一直執行,所以無法減低功耗。因此使用Microchip CIP (Core Independent Peripherals}所提供CLC (Configurable Logic Cell)再加上CCP (PWM) with Timer的功能,即可非常容易的用純硬體架構來實現LFSR功能,解決當應用場合非常注重高速信號、Jitter及功耗的情況。

-個最基本的Microchip GIP CLC架構 如圖三所示,可以把它想成是-個可設定的組合/時序邏輯的總成。CLC的輸入可以是可選擇的多個 10腳位,也可以是 其它週邊的輸出信號,或是 Clock 信號。而這些不同的輸入信號 可以經由被指定的組合/時序邏輯匯整處理後再來輸出到不同的10, 或者也可以按照使用的設計再輸出到下一級的CLC/Peripherals去,同時也能產生 interrupt , 讓CPU介入處理,如圖四所示。在這裡要特別強調的是,它是純硬體的動作!快速省電並且不需要CPU 去執行軟體-直做介入,一但設定完成CLC及CCP即可持續動作,CPU即不用-直花費資源及功率在CLC及CCP的運作上,可以把CPU的資源用在其它需要的工作上。

所以在Microchip PIC16F177X的MCU系列中,它的週邊設置(圖五),具有四個的CLC 以及CCP, 因此可以設定成4 bit的LFSR再利用CCP模組產生的WM 信號來做LFSR的同頻信號。而 CLC跟CCP的設置也非常的簡單,只要透過 MPLA的XIDE with MCC的使用者開發介面,以勾選或填值的方式來自動產生程式碼即可,因此對於非程式設計背景的使用者也非常方便切入進行相關的實作。

如需瞭解更多資訊請至網站 http://www.microchip.com

作者吳建瑩為 Microchip 工程師