在『封裝五大法寶』的第四部分,我們比較了傳統的系統級封裝SiP與先進的基板級系統封裝SiP,先進的基板級系統級封裝已成為一種突破性的規則改變者,在射頻、固態硬碟、汽車、物聯網和功率市場,提供性能上系統級的集成,提供最佳的性價比。在最後的這第五個部分,我們繼續往下看,晶圓級的系統級封裝,它將如何推動半導體行業進入下一個萬物互聯的時代。

如同基板級的系統級封裝,晶圓級的系統級封裝也是整合複雜和不同技術的晶片,甚至提供了更高的性能,更高的頻寬和更小的尺寸。目標是高效能運算電腦、物聯網、手機和汽車行等領域。除了整合,微處理器、感測器、射頻和電源管理晶片,先進的晶圓級的系統級封裝,更能集成高頻寬記憶體(HBM,HMC),ASIC,高性能運算的圖形處理單元(GPU)和FPGA。

晶圓級的系統級封裝

Amkor認為『封裝五大法寶』是:低成本覆晶封裝(Low-Cost Flip Chip),晶圓級晶片尺寸封裝(WLCSP)、微機電系統封裝(MEMS Packaging),基板級的系統級封裝(Laminate-based SiP), 和最後一部分,是晶圓級的系統級封裝(Wafer-based SiP),這可能是將來服務應用範圍最廣的技術。

晶圓級的系統級封裝,目前還處於早期階段,優先導入到相對高端的元件。它有效地解決了系統的擴展需求,延緩晶片推進到下一世代矽節點的壓力。其最早的切入點是高性能計算(HPC),記憶體和高端移動裝置。然而,隨著時間的推移,我們相信更多的設備將利用此技術,使之外觀尺寸減少,並降低功耗,增加性能。

相較於基板級的系統級封裝是利用現有的晶片封裝技術為基礎,然而,晶圓級的系統級封裝的製造過程,將有非常顯著的不同,需要投資新的機台設備。晶圓級的系統級封裝將替代/或補充原有的基板,提供重分佈層(RDL),並將目標線寬/線距(L / S)藍圖推進到1μm / 1μm。 此重分佈層的能力,將達到晶圓廠後段製程工藝(Fab BEOL)的級別,相較於傳統的基板,其線寬/線距(L / S)極限僅能達到10μm / 10μm 。因此,晶圓級系統級封裝,是目前微縮能力最好的解決方案,也是唯一具有晶圓廠製程能力級別的解決方案。

Amkor研發副總裁Ron Huemoeller,已經在許多半導體行業論壇,介紹將多顆不同技術晶片整合進更小封裝體的技術,就是晶圓級的系統級封裝技術。在Amkor,我們正集結大量的知識和能力研發這類技術,如SWIFT 和 SLIM,從封裝和板級的可靠性測試結果,我們的SWIFT封裝技術已正式進入試產階段。

由於工藝的難度和複雜性大幅提高,晶圓級的系統級封裝製造成本也將隨著增加。成本的提高有一大部分是在初期的資本支出投資(Capex),如建立class 1或class 10的無塵室工廠,投資購買像晶圓廠級別的新設備,如物理/化學氣相沉積(PVD/CVD),化學機械研磨(CMP),暫時貼合/分離(Temporary Bond/Debond)的機台設備,這些必須的先期投資,隨著工廠和機台的攤提折舊,生產成本會再進一步降低,到那時將是這項技術大放光芒的時機。

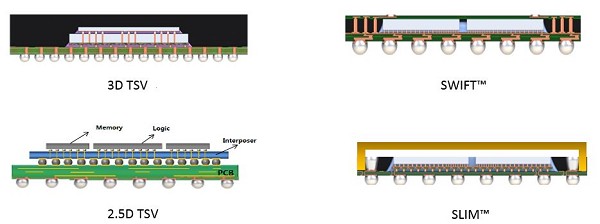

在晶圓級的系統級封裝的家族,包括高密度的扇出晶圓級封裝,如Amkor在SWIFT/SLIM產品線。Amkor 在這技術中使用了具有良率優勢的“Die Last”的製程程序,相較於”Die First”的製程程序”,此技術能避開數層RDL的不良率風險,因此會有更高的最終良率。目前SWIFT/SLIM小尺寸產品已經通過了CPI驗證,大尺寸的在積極研發中,預期幾個季度內將大量生產。Amkor的先進系統級封裝技術藍圖中,還有2.5D interposer 和 3D IC,2.5D的TSV產品已經在2013年驗證生產,我們已和上下游策略夥伴建立一個協同的Ecosystem,目標不只是提供生產,更要提供客戶相關設計套件,建立完整晶圓級的系統級封裝平台。

| 圖2 : Amkor’s wafer-based SiP offering. ( source: Amkor ) |

|

結論

總之,手機和移動市場驅動了更多晶片更高集成度,整合到更小尺寸的封裝體,而在高速計算,深度學習,和圖形運算處理領域,晶圓級系統封裝更著重在解決功耗,頻寬,和時序延遲的速度問題,預期在接下來的幾年,2.5D IC,3D IC,SLIM, SWIFT 等技術發展,將有機會藉由先進封裝技術延續著摩爾定律的推進。晶圓級的系統級封裝,完成了Amkor封裝五大法寶的組合。

(作者Rama Alapati為Amkor副總裁,本文原載於3D InCites)