製程餘裕較小的先進技術節點需要改進微影疊對的管制。基於光學量測目標的研發檢測(DI)時的疊對管制在半導體製造中已經頗具規模。在目標設計和量測技術方面的進展,使疊對的精確度和準確度都得到了大幅提升。表示晶片內裝置上蝕刻疊對的一種方法就是在最終檢測(FI)時,使用掃描電子顯微鏡(SEM)進行測量。這種方法的劣勢在於無法返工和疊對的層覆蓋有限,這是由於缺乏透明及經營成本(CoO)較高。

本報告研究了一種混合方法,將不頻繁測量的 DI/FI 偏差進行表徵,且把其結果用於補償頻繁測量的 DI 疊對結果。這個偏差表徵並不是頻繁進行,可基於時間,或者由轉變點觸發。在按元件和按層的基礎上,將DI 的光學目標疊對與 FI 的 SEM 的元件上的疊對進行比較,對兩者的偏差表徵結果進行驗證并跟蹤,用於補償 DI APC 控制器。本文介紹 DI/FI 偏差表徵結果和變化來源,並介紹對DI調整饋送 APC 系統的影響。本文回顧該方法在大批量製造(HVM)晶圓廠的實施詳情,並在文章最後將討論該研究的未來方向。

簡介

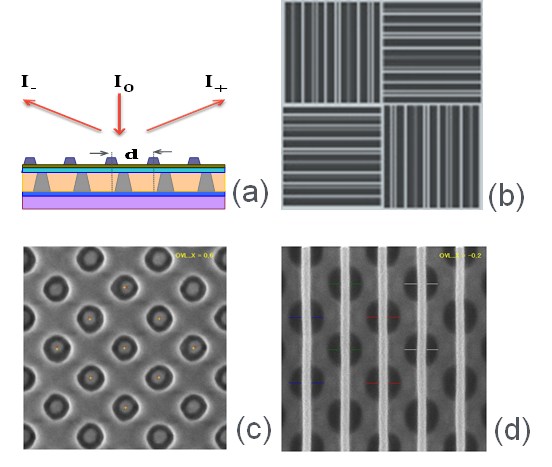

在先進的半導體生產中,疊對已經成為最關鍵的參數之一。大批量製造(HVM)製程管制主要基於對特別設計目標的光學量測,這些目標通常位於劃線區或晶片間切割道內。量測通常會在開發檢測(DI)中執行,也就是在微影工序之後。該檢測方案的優勢包括高產能量測、對光學量測的層透明,以及返工能力。圖 1a 和 1b 展示了疊對量測方式的典型例子。散射量測疊對(SCOL)和帶有先進成像量測(AIM)標記的成像疊對。由於偏移檢測和先進製程管制(APC)的需求,DI的量測會以較高頻率完成,通常會檢測所有關鍵層的每一個批次。

在蝕刻後,疊對量測以低得多的頻率在最終檢測(FI)時執行。FI 疊對儘管沒有DI 那麼常見,但是通常會使用掃描電子顯微鏡(SEM)的技術在元件結構上完成,而不是在如圖1c 和1d中顯示的特別設計的量測目標上完成。使用SEM進行FI 疊對的劣勢,包括低產能和因此導致的高成本、以及某些層缺少透明度,因而在某些情況下需要開蓋去層工序,並無法對不合規格的材料進行返工。

| 圖1 : 疊對量測範例:(a)散射測量疊對(SCOL)圖解、(b)先進成像量測 (AIM)標記,(c)以及(d)SEM 裝置上示例。 |

|

進入到 1x DRAM 製程要求在 HVM 中有 2 nm 的疊對規格。就像通常前進到新的設計節點一樣,必須解決新的變量所帶來的問題。對於已經透過手動方式或偶爾需要解決的問題,可能需要更為頻繁的更新、更多的自動化,以及更好的分析工具。量測標記上的 DI 疊對和元件結構上的 FI 疊對之間的 Δ 在很多節點上需要被關注。新的問題是, DI-FI 偏差的相對大小,通常在光罩(或視場)級別以及晶圓級別上都要遠遠大於 2 nm的 OL 規格。

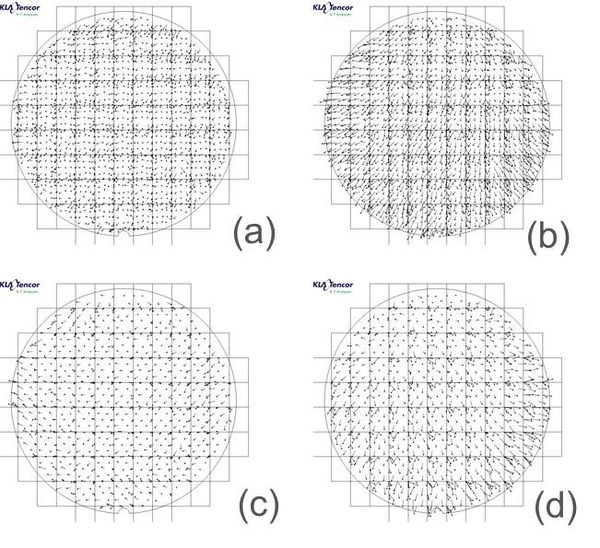

| 圖2 : 晶圓圖顯示:(a)有製程校正的 DI 疊對,(b)無製程校正的 DI 疊對,(c) FI 疊對,以及(d)DI-FI 偏差。 |

|

圖 2 顯示了 DRAM“A 層” 的DI-FI 偏差的範例。圖 2a 顯示了有製程校正的 DI 疊對,2b 顯示了無製程校正的 DI 疊對。兩種 DI 結果都是基於劃線量測目標的光學量測。圖 2c 顯示出 SEM 測量的裝置結構上的 FI 疊對,而最終圖 2d 則顯示了 DI-FI 偏差,即 DI 疊對(無製程校正)與 FI 疊對之間的差異。

儘管使用 SEM 疊對量測存在?顯著的錯誤和偏差機會,但是為了本項工作的目的,我們假定 SEM 所測量的 FI 疊對即是為最優化裝置性能目的而應當儘量減少的疊對誤差。透過調整 DI 的非零偏移以將裝置上的FI疊對降至最低的方案,稱為非零偏移(NZO)。對用於1x nm DRAM 節點所必需改善的製程管制,目標是(1)表徵 NZO、(2)儘量降低 NZO、(3)儘量降低 NZO 可變性,以及(4)標識 NZO 偏差。為了達到這樣,需要最佳的目標設計 [1]、優化的量測配方 [2]、跟蹤偏移的能力,以及自動表徵和更新 NZO 的系統。本工作的重點是 NZO 的自動化和表徵,以改善製程管制。

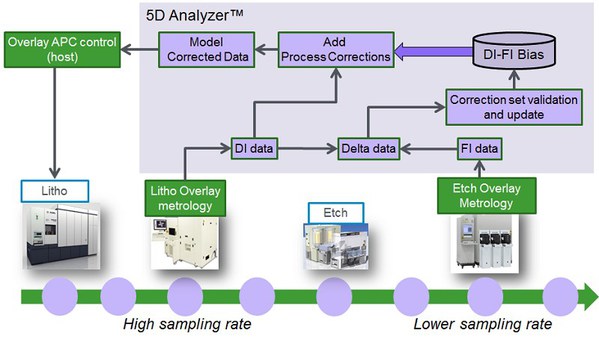

| 圖3 : 使用 KT Analyzer 進行的自動化製程校正更新方案。 |

|

圖 3 顯示了 一個NZO 管制方案的示意圖。在微影疊對後基於光學的高頻率 DI 管制回路之後,以蝕刻后的低頻率 FI 更新作為輔助。FI 更新的觸發點可包括製程改變點(例如製程工具預防性維護或 PMs),使用時間,或者基於偏移。一旦觸發,通過FI 和 DI的數據值的差值,以得到偏差,隨後進行建模和存儲。 NZO 偏差被用來糾正 DI 製程回路。這樣,高頻率 DI 管制回路可有效地針對非零疊對,以使FI 疊對達到最小。當我們採用更先進的製程節點時,NZO 製程就需要更好的自動化、更好的分析,以及更好的製程管制。

在本研究中,我們觀察了兩個 DRAM 層的 NZO。在一個案例中,我們使用記錄程序 (POR) 取樣,調查批次至批次之間的變化和疊對預算細分。在第二個試驗中,我們觀察了單個晶圓上的完整圖取樣。

批次至批次之間的預算細分

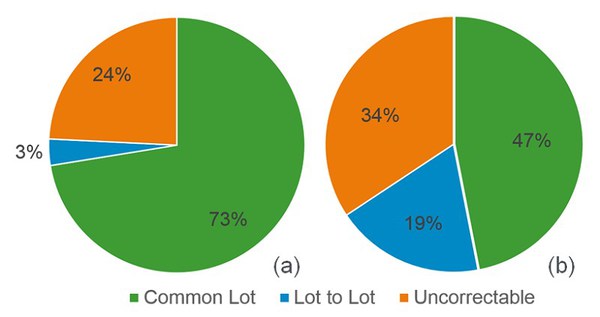

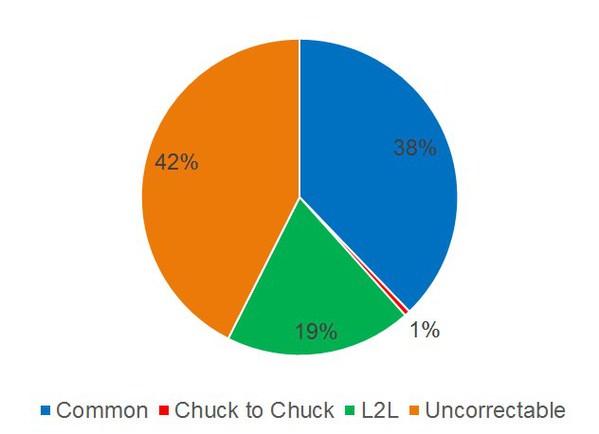

上述 NZO 管制方案要求每次更新之間的 DI-FI 偏差相對穩定。在我們的第一個研究中,觀察了批次至批次之間的DI-FI 偏差之變化。在本例中,研究了A 層 3 個批次的單夾盤資料,每個批次一片晶圓,以及在數周時間內採集的 B 層 14 個批次的雙夾盤資料。變量來源分析涉及使用 W3F3 模型進行的晶圓建模,即跨視場和跨晶圓的三階模型,這是典型的先進管制方案。圖 4 顯示了 A 層和 B 層的變量來源分析。在這些例子中僅顯示了X 疊對,因為它是用於管制的最關鍵的軸向。對於 A 層,我們看到在實驗過程中,大多數的變化在整個批次中都很普遍。一小部分為批次至批次之間的變化。最終,一小部分變化未能被 W3F3 模型所捕獲。B 層的情況也類似,但是批次至批次之間的變化和未建模的部分在該案例中佔有更高百分比。

| 圖4 : (a) A 層和 (b) B 層 X 疊層對準變量分析的 DI-FI 偏差來源。 |

|

圖 5 顯示了對 B 層的補充分析,其中 8 片晶圓來自夾盤 1,6 片晶圓來自夾盤 2。在本例中,在變量分析中增加了夾盤至夾盤的變化。不出意料,我們看到夾盤至夾盤之間的變化相當小,因為預計的 DI-FI 偏差主要是來自非微影來源,如蝕刻或沉積。

| 圖5 : 包括卡盤至卡盤在內,用於 B 層的 X 疊層對準的 DI-FI 變量分析的偏差來源。 |

|

全圖分析

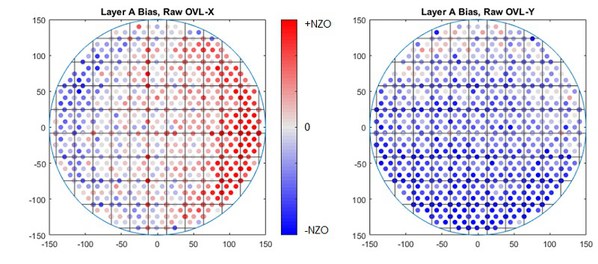

在第二項研究中,分析了來自單個晶圓的全圖疊對資料。圖 6 顯示了全圖 DI-FI 偏差未建模指紋。如圖所示,偏差通常是跨晶圓效應而不是跨視場效應,這並不奇怪,因為預期的偏差通常是來自於微影之外的工序。在這種情況下,看到的變化是接近晶圓級別的特徵。

| 圖6 : 適用於 A 層的全圖 DI-FI 偏差,顯示原(未建模)特徵。 |

|

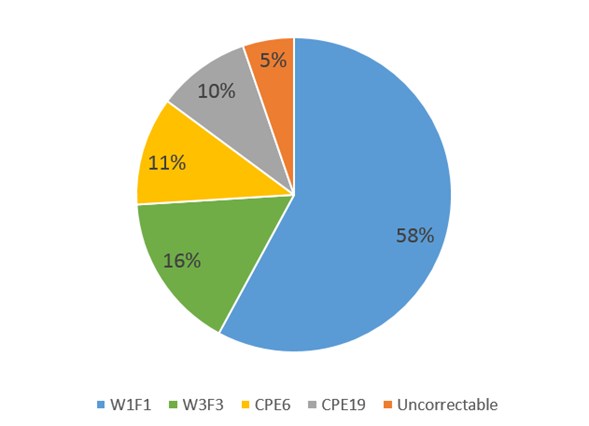

進一步分析 A 層全晶圓 DI-FI 資料,依次使用更高階模型建模來進行變量來源分析。如圖 7 所示,可以看到,大多數變化都可以透過線性模型 W1F1 進行表徵。僅次於它的一類變化可透過三階模型 W3F3進行表徵。最終,我們應用了 CPE6 和 CPE 19 模型,即每個視場分別有 6 個和 19 個項目。可以看到,超出高階 W3F3 POR 模型的很大一部分變化都可以用 CPE 捕獲。

| 圖7 : 包括 CPE 在內的 A 層全圖 DI-FI 變量分析偏差來源。 |

|

結論

DI-FI 偏差在許多節點上已經成為製程管制的一部分。新的問題是相較於疊對規格的 NZO 的相對大小,以及找到更完整解決方案的需求,以便對 NZO 的變化進行表徵和最小化。在本研究中,我們研究了根據低頻率 FI 更新在 DI 管制回路中自動更新NZO。我們展示了在數週時間內,大部分 DI-FI 偏差在批次與批次之間的變化是普遍的,但是在某些層批次至批次之間的變化也可以非常顯著,因此需要仔細考慮。我們目前進一步工作,是儘量減少 NZO,儘量減少 NZO 變化、跟蹤 NZO 偏移,并提供最佳 NZO 製程管制。

(本文作者Honggoo Lee、Sangjun Han、Youngsik Kim於SK Hynix;Myoungsoo Kim於Dept. of Semiconductor System Engineering, Korea University;Hoyoung Heo、Sanghuck Jeon、DongSub Choi 於KLA-Tencor Korea;Jeremy Nabeth、Irina Brinster、Bill Pierson、John C. Robinson於KLA-Tencor 公司)

參考文獻

[1] Wei Jhe Tzai、Simon C. C. Hsu、Howard Chen、Charlie Chen、Yuan Chi Pai、Chun-Chi Yu、Chia Ching Lin、Tal Itzkovich、Lipkong Yap、Eran Amit、David Tien、Eros Huang、Kelly T. L. Kuo、Nuriel Amir,《透過使用裝置相關的量測目標為參考,改善疊層對準精準度的方法》(“Techniques for improving overlay accuracy by using device correlated metrology targets as reference”),J. Micro/Nanolith。MEMS MOEMS 13(4)、041412(2014 年 10 月至 12 月)。

[2] Honggoo Lee、Byongseog Lee、Sangjun Han、Myoungsoo Kim、Wontaik Kwon、Sungki Park、DongSub Choi、Dohwa Lee、Sanghuck Jeon、Kangsan Lee、Roie Volkovich、Tal Itzkovich、Eitan Herzel、Mark Wagner、Mohamed ElKodadi,《對先進記憶體裝置進行的疊層對準精準度調查》(“Overlay Accuracy Investigation for advanced memory device”) Proc. of SPIE Vol. 9424,2015 年