隔離使用者和敏感的電子裝置,已經成為馬達控制系統中一項重要的考量因素。安全的隔離可保護使用者避開傷人的高電壓,同時機能性的隔離也著重在保護設備和元件。馬達控制系統可包含多種隔離元件,在驅動電路(隔離型閘極驅動器)、感測電路(隔離型ADC、放大器、感測器),或在通訊電路(隔離型的SPI、RS-485、標準數位隔離器),而用心選擇這些元件非常重要,不僅是為了安全,還可以讓性能最佳化。

隔離做為一項重要的系統考量,並非沒有以下缺點:功率的增加,通過隔離屏障傳送資料的延遲,以及額外的系統成本。系統設計人員在傳統上傾向以光耦合器為基礎的解決方案,多年來也都是系統隔離的實際選擇。數位隔離器則是一種以磁能為基礎的方法(由變壓器傳輸),在過去十年中提供了一個可行的,而且往往是高等級的替代方案,當在系統層級考量下,所提供的優點並非能讓系統設計人員察覺得到。

本文將著眼於這兩種解決方案的隔離要求,特別著重以磁能為基礎的隔離,在測量延遲時間所提升的性能,並累積在馬達控制應用由此產生後續系統層級的優勢。

隔離的方法

光耦合器以光線作為主要的傳輸方法,如圖1所示。發射端包括一顆發光二極體,其中高位準信號將LED開啟,而低位準信號將其斷開。在接收端,光檢測器用來將接收的光轉換回電信號。隔離是由LED和光檢測器之間的模塑料(mould compound)來做,但也可以用額外的隔離層(通常是聚合物型)來加強。

關於光耦合器有一項很大的缺點,就是隨著LED的使用年限,其發光特性會漂移,造成設計人員必須去考慮的一項額外問題。LED隨著時間和溫度的退化,會導致時序的漂移。因此,傳輸和信號上升/下降時間會受到影響,而使得設計更加複雜,特別是本文稍後所處理的情況。

光耦合器也苦於測試性能擴展性不足的問題。為了提高資料傳輸速率,必須克服光耦合器固有的寄生電容,這會增加功率消耗。寄生電容還會提供一個耦合機制,導致光耦合器型隔離器的CMTI(共模暫態免疫性)性能比競爭對手還差。

磁能隔離(以變壓器為基礎)已用於量產應用十多年了,是一種替代光耦合器的可靠方案。這些都是以標準CMOS製程為基礎,以及隔離層使用聚醯亞胺或二氧化矽所組成,如圖2的磁傳輸方案。低量電流以脈波型式通過線圈,產生一個磁場,穿過隔離屏障並在屏障另一邊的二次側線圈上感應出電流。由於使用標準的CMOS結構,可以憑藉功率和速度取得顯著的優勢,此外,也避免了與光耦合器相關的壽命變異問題。而且由於目前變壓器型隔離器的寄生電容較低,因此也比光耦合型隔離器提供更好的CMTI性能。

變壓器型隔離器還可以使用共模處理方塊,來防止傳輸過來的寄生輸入,以及先進的傳輸編碼解碼機制。這允許雙向資料傳輸,使用不同的編碼方案來使功率對傳輸速率最佳化,並讓重要信號更快且更加一致的通過隔離屏障來傳送,這在本文的餘下部分將討論之。

延遲特性的比較

所有隔離的關鍵特點之一是傳輸延遲,但其往往被低估。這裡測量了發出信號通過隔離屏障(在任一方向,因此既可以是一個驅動信號,也可以是一個故障檢測信號)所花費的時間長度。由一種技術更換成另一種技術,其傳輸延遲的變化很顯著。雖然通常提供的是典型延遲值,然而對於系統設計人員而言,特別會關切的是最大延遲,在設計馬達控制系統時,這是必須考慮的關鍵規範。表1提供了關於光耦合型和磁能型隔離閘極驅動器,其傳輸延遲值和延遲失真值的例子。

表1:光耦合型與磁能型隔離器的典型延遲特性

隔離類型 |

最大傳輸延遲 |

傳輸延遲失真 |

光耦合型 |

高達700nS |

200nS |

磁能型 |

60nS |

12nS |

如表1所示,磁能型隔離在最大延遲與延遲的重複性(歪斜失真)這兩項有顯著優勢。這讓馬達控制的設計人員在設計上更有信心,由於降低了為時序規格加大容限的需求,因此更能滿足閘極驅動器的特性。這對馬達控制系統的性能和安全性有非常重要的影響。

馬達控制系統的系統涵義

用於交流馬達控制應用中的一種典型三相倒相器,如圖3所示。倒相器由直流匯流排所提供,通常可以直接從交流電源通過二極體橋式整流器與電容或電感─電容濾波器來產生。在大多數工業應用中,該直流匯流排電壓的範圍從300V至1000V。一股可變電壓、可變頻率的三相正弦波交流電壓,藉由以5-10kHz的頻率的脈寬調變(PWM)方式來開關功率電晶體T1-T6,而在馬達端子上產生。

PWM信號(PWMaH、PWMaL等)是由馬達控制器內部產生,通常是以處理器和/或FPGA來實作。這些信號通常是參考到處理器接地軌的低電壓信號。為了正確地導通和斷開功率電晶體,這些邏輯位準的信號必須將電壓位準與電流源能力都放大。而且也必須做位準移位,使得其對地參考到相關功率電晶體的射極。取決於系統內處理器的位置,它們也可能需要做安全等級的絕緣。

這些功能是由閘極驅動器(在圖3中的GDRVaL/ GDRVaH等)進行。各閘極驅動器IC將需要一個參考到處理器接地端的一次側電源電壓,以及一個參考到電晶體射極的二次側電源電壓。二次側電源會需要有一組能夠導通功率電晶體的電壓位準(通常為15V),和足夠的電流驅動能力以對電晶體閘極進行充電和放電。

倒相器空白時間

功率電晶體有一段有限的開關時間,而因此在高端和低端電晶體之間,脈衝寬度調變的波形上,必須插入一段空白,或稱為「空白時間(dead time)」,如圖4所示。這是為了防止兩顆電晶體意外的被同時導通,因此造成高壓直流匯流排的短路,導致系統故障和/或損壞的風險。空白時間的長度由兩個因素決定─電晶體的開關時間,以及閘極驅動器傳輸延遲的不匹配(包括不匹配時的任何漂移)。換言之,空白時間必須考慮在PWM信號傳輸時間,從處理器到電晶體閘極,高端和低端閘極驅動器之間的任何差異。

空白時間的影響是使得施加到馬達(特別是在低速時)的平均電壓失真。空白時間實際上投入了一個約為定數的幅值誤差電壓[2]。誤差電壓在一個相位的電流改變方向時會改變符號,還有當馬達線到線電壓在線電流越過零的點上,會發生步階變化。這會產生正弦基波電壓,進而在馬達上產生電流諧波。這對使用開迴路驅動,較大的低阻抗馬達而言,這是一個特殊的問題,其中所述諧波電流會很顯著的導致低速振動、轉矩漣波和諧波發熱。

空白時間對馬達輸出電壓的失真影響,在最壞的情況會有以下狀況:

‧ 提高直流匯流排的電壓

‧ 加長空白時間

‧ 提高開關頻率

‧ 導致低速操作,特別是在開迴路的驅動下,控制演算法中沒有加入任何補償時

低速操作是很重要的,因為在這種模式中,各種情況施加於馬達的電壓都很低,而且從空白時間得來的誤差電壓,將成為施加於馬達電壓上的顯著因子。此外,在低速時,任何引發的轉矩漣波都具有更不利的影響,因為在較高速度下系統慣性為有效的濾波在此是無效的。

在所有的參數中,空白時間的長度是唯一一個可以由隔離閘極驅動器的技術來影響的參數。某些空白時間的長度是由功率電晶體的開關延遲時間來決定,但是其餘的則為傳輸延遲不匹配的函數。在這種情況下,光學型的隔離器與磁能型隔離技術相比存在顯著的劣勢。

範例應用

為了說明空白時間對馬達電流失真的影響,以開迴路馬達驅動為基礎的3相倒相器,其結果如圖示。使用ADI(ADuM4223)磁能隔離器於所述倒相器的閘極驅動器,直接驅動IR(國際整流器公司)IRG7PH46UDPBF 1200V IGBT。直流匯流排電壓為700V。該倒相器以開迴路V / f控制模式來驅動三相感應馬達。線到線電壓與相電流用電阻分壓器和分流電阻,與隔離型Σ-Δ調變器一起來量測,一樣是ADI(AD7403)。單一位元資料流從每個調變器被饋送到控制處理器(ADI的ADSP-CM408)的SINC濾波器,在此資料被濾波、消化,以產生精確的電壓和電流信號表示值。

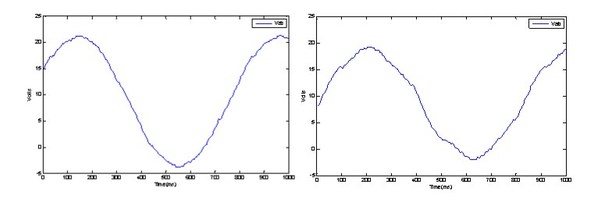

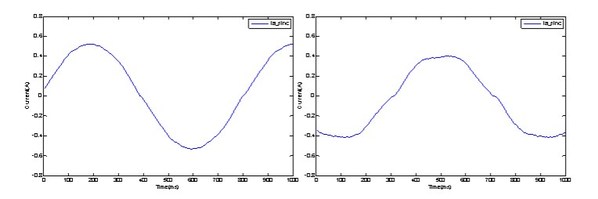

從SINC數位濾波器輸出端所測量的線到線電壓值,如圖5所示。實際的線對線到線電壓是10kHz的高頻開關波形,但會由數位濾波器濾除,讓想了解的較低頻成份可視化。後續的馬達相位電流如圖6所示。

由於與ADuM4223閘極驅動器的傳輸延遲不匹配是12ns,所以有可能在IGBT開關上使用絕對最小空白時間。在IR IGBT的例子中,最小空白時間則可設定成500ns。從左側的圖中可清楚了解,在這種情況下,電壓失真為最小。同樣地,相電流非常近似正弦波,這可得到最小的轉矩漣波。右側的圖指出線到線電壓和相電流與空白時間增加至1s。這個值更具代表性的顯示,光學耦合閘極驅動器由於其較高的傳輸延遲不匹配和偏移,會更需要什麼。在電壓失真,以及隨之而來電流失真的增加,是顯而易見的。在這種情況下,所使用的感應馬達是一個比較小的,高阻抗的機器。在較高功率端的應用中,感應馬達的阻抗通常是低得多,將進而增加馬達電流失真和轉矩漣波。轉矩漣波在許多應用中,都會產生不利影響─例如電梯的乘坐舒適性會降低,或機械系統的軸承和連軸器會磨損。

| 圖5 : 量測線到線電壓於(左)500ns空白時間(右)1μs空白時間 |

|

| 圖6 : 量測馬達電流於(左)500ns空白時間(右)1μs空白時間 |

|

過電流斷開

現代閘極驅動器的另一個重要問題,是處理器發出斷開命令到IGBT的實施速度。這在過電流關機的情況之下很重要,其中過電流檢測並非閘極驅動器本身的一部分,而是實做為感測和濾波電路的一部分。在這方面附加的壓力是縮短了高效率IGBT的短路耐受時間。為此IGBT技術的趨勢是從工業標準10μs減少到5μs ?[3],甚至更低。如圖7所示,過電流檢測電路將通常要花幾微秒到閂鎖故障─接下來要去減少檢測時間,以適應總體趨勢。路徑中的另一個主要元素是從處理器/ FPGA輸出到IGBT閘極─即閘極驅動器的傳輸延遲。再一次,磁能隔離器比起光學元件提供了一個顯著優點,在磁能隔離器上,由於值非常低,通常落在50ns內,傳輸延遲實際上是非因子。反之,光耦合器有傳輸延遲為500ns,這表示其佔有整體時序預算的顯著比例。

馬達控制應用中的閘極驅動器斷開時序圖示於圖8,其中從處理器發出斷開命令(CH1)顯示於圖上,緊跟著是IGBT閘極─射極信號(CH3)。由斷開信號開始到IGBT的閘極驅動信號接近零的點,總延遲只有72ns。

總結

隨著馬達控制設計越來越重視系統的性能、效率和安全性,設計人員在設計強固的系統時,面臨更加複雜的任務。雖然光耦合器型的閘極驅動器一直是傳統的選擇,變壓器型的解決方案卻能提供功率、速度和整個穩定性方面的優點,也以減少信號延遲提供效能和安全性等顯著的優點。這讓設計人員能夠有自信的減少空白時間,提高系統性能,同時還避免高端和低端開關同時導通。此外,對系統命令和錯誤的響應更快,再次增強了系統的可靠性,同時提高安全性。這些優勢將以隔離式閘極驅動器為基礎的變壓器成為馬達控制系統設計的主要選擇,並建議系統設計人員在他們的下一個專案中,應該認真考慮將元件的延遲做為一項關鍵的要求。

(本文作者Dara O’Sullivan為ADI亞德諾半導體馬達與功率控制事業群系統應用工程師;Maurice Moroney為ADI亞德諾半導體iCoupler數位隔離器事業群行銷經理)

參考資料

[1] Krakauer, David, Balancing the Major elements of an Isolator for Safety’s Sake, ADI Technical Article MS-2576, www.analog.com

[2] Munoz,A.R. and Lipo, T.A., “On-Line Dead-Time Compensation Technique for Open-Loop PWM-VSI Drives”, IEEE Transactions on Power Electronics, vol.14 no.4, July 1999.

[3] http://www.onsemi.com/pub_link/Collateral/NGTB15N60S1E-D.PDF