@引言:觀察FPGA產業的市場變化, 儘管擁有相當高的靈活度的技術優勢,

但從單一到多點節點製程,不難想見,FPGA也必須廣泛地滿足市場需求。

@QUOTE:

不論是賽靈思或是Altera,競相投入先進製程的開發,

或許彼此之間互有領先,但能夠證明先進製程FPGA強大效能的終端應用,

似乎只剩大型通訊基地台而已。

2013年11月11日,賽靈思(Xilinx)推出業界首款20奈米的KintexR UltraScale? XCKU040 All Programmable FPGA元件,遠比競爭對手提早數月上市。隨後在同年12月,賽靈思接著推出 20奈米 Kintex UltraScale和VirtexR UltraScale 產品系列,後者產品系列包括Virtex UltraScale VU440。此款元件採用3D IC技術、內建440萬個邏輯單元,打破了由賽靈思28奈米製程的 Virtex-7 2000T FPGA元件,所保持的最高容量和最多半導體電晶體數之世界紀錄。

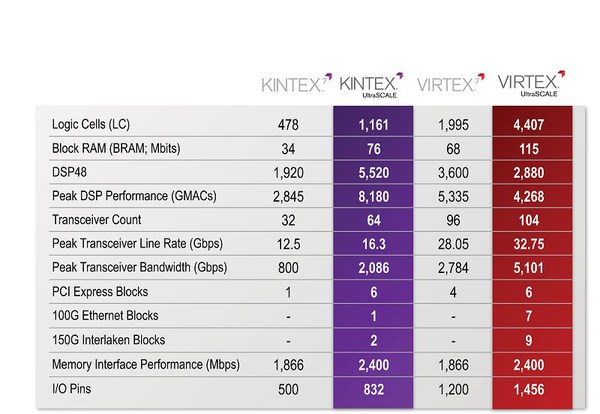

賽靈思企業策略與市場行銷資深副總Steve Glaser表示,我們已開始經營20奈米製程的業務並推出多款20奈米的UltraScale元件。20奈米UltraScale的推出進一步穩固了原先28奈米 7系列All Programmable元件所創立的市場領導地位。他也指出,目前我們推出了業界首款採用台積電(TSMC)公司 20SoC製程的20奈米元件,且採用業界最先進的晶片架構以及ASIC加強型設計套件與方法。」所有20奈米製程的 Kintex UltraScale和 Virtex UltraScale 產品系列元件都具備ASIC級的效能與功用,與賽靈思7系列中的相對應產品相較,具有更低的功耗和更高的容量(如圖1)。

| 圖一 : 相較於Kintex和Virtex 7系列元件,20奈米Kintex和與Virtex UltraScale FPGA具有眾多業界的領先規格,(已列出最大數量)。 |

|

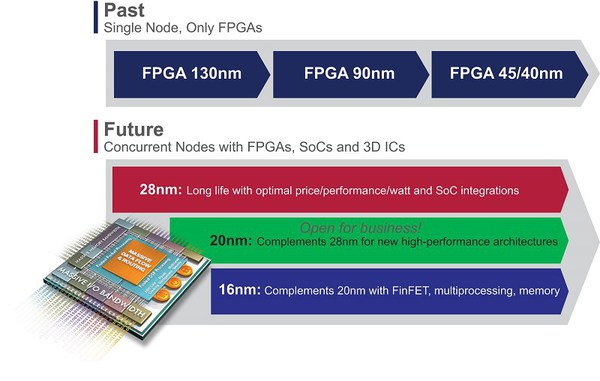

目前,28奈米的 7系列在可編程邏輯元件的全球市場占有率超過70%。此外,賽靈思也進一步提升UltraScale元件架構,並對VivadoR設計套件進行多項ASIC級的改善。2013年10月,賽靈思推出UltraFast Design Methodology 的最新設計方法。繼推出20奈米 UltraScale產品系列後,賽靈思將接著以多節點策略推出16奈米FinFET UltraScale元件(如圖2)。

| 圖二 : 賽靈思的領先一代策略,注重多節點產品開發,推出多款各節點FPGA、SoC和3D IC產品線滿足客戶需求。 |

|

賽靈思產品線市場行銷經理Kirk Saban也談到,現今為多製程節點的時代,客戶會依其系統需求來決定選用7系列、20奈米的UltraScale或即將推出的UltraScale 16奈米 FinFET系列做為合適的設計元件。如果將20奈米的 Kintex UltraScale元件與Kintex-7元件相比,我們會發現Kintex UltraScale 的邏輯單元數量與DSP功能明顯強於Kintex-7。這是因為Kintex的價位和元件密度可滿足目前絕大多數需要高訊號處理頻寬的應用。如果客戶的應用不需較高的密度或更強的DSP功能,那麼Kintex-7仍是非常適合的設計元件。

Kirk Saban表示,多節點方案的作法,讓市場可以選擇最為廣泛的All Programmable元件,同時Vivado設計套件和UltraFast方法可實現相當高度的高生產力。這些先進元件都建立在堅實的製造技術基礎之上。 我們擁有業界最強大的晶圓代工合作夥伴,在產品交期與可靠度方面都令人信服。台積電公司前CTO,現任顧問胡正明(Chenming Hu)先生是FinFET製程的先驅,在新一代FinFET製程的技術開發給賽靈思留下了非常深刻的印象。

Kintex與Virtex UltraScale電晶體數量

每種晶片製程節點都會為半導體產業帶來全新的製造與設計挑戰,而20奈米製程也不例外,尤其是在佈線延遲、時脈誤差和可配置邏輯塊(Configuration Logic Block;CLB)封裝等方面更是如此。然而, Kintex UltraScale和Virtex UltraScale元件可克服這些難題,大幅提高整體效能與利用率。這種錯綜複雜的節點使賽靈思能夠對架構進行多項模塊層級的改進,並可與Vivado工具套件實現共同最佳化,提供最高頻寬和最大訊號處理能力。

如果仔細觀察DSP方面的技術進展,就會發現UltraScale已經採用更寬輸入的乘法器,有助於在每個功能上使用較少的模塊並為各種DSP應用提供更高的精準度。而且還在DSP48內部為無線通訊客戶,在FEC(前向錯誤修正)、ECC(錯誤更正碼)和CRC(循環冗餘校正)等三方面增加了一些新特性。

賽靈思在Block RAM方面加強了資料串聯輸出,並利用一些全新的創新功能,改善功耗和提升BRAM效能。

賽靈思在20奈米製程的 Kintex和Virtex UltraScale產品系列中提供兩種不同的收發器。中/高速度級Kintex UltraScale元件支援16.3Gbps底板運行。即使Kintex UltraScale系列中速度最低的元件也具備出色的12.5Gbps收發器效能,這對無線應用來說尤其重要。同時,賽靈思Virtex UltraScale產品可提供28Gbps背板運作功能以及33Gbps晶片至晶片,以及晶片至光學介面效能的收發器。

在UltraScale中加入一些重要的整合IP硬核模組,如將100Gbps乙太網MAC作為IP硬核增加到Virtex和Kintex UltraScale系列元件中。此外,在這兩個UltraScale產品系列中新增工作效能高達Gen3x8的150 Gbps Interlaken介面和PCI ExpressR Gen3硬核模組。UltraScale系列均支援DDR4記憶體,可提供比7系列元件高40%的資料速率,同時使記憶體介面的總體功耗降低20%。

Kirk Saban指出,在安全方面,賽靈思添加多項特性以提供更強的密鑰保護能力,執行更加詳細且複雜的認證方案,而Vivado工具套件可支援這些最新的加強功能。他提到,Virtex和Kintex UltraScale元件享有相同的架構效能。但Kintex UltraScale單就其密度而非效能方面而言,屬於中階FPGA。

最後同樣重要的一點是,20奈米的 UltraScale建立在賽靈思相當成功的3D IC技術基礎之上,而該技術在7系列產品中已率先使用。利用第二代堆疊式矽晶互連(SSI)技術,透過多晶片(multidice)技術提升晶片間的頻寬,實現重大的效能提升。Kirk Saban談到:SSI技術可使多晶片成為一個整體在超大元件中運作,實現單晶片元件設計。而賽靈思利用SSI技術再一次突破自己所保持的最大容量FPGA和最高IC電晶體數量。

創世界記錄的容量

20奈米UltraScale產品系列中的明星當屬Virtex UltraScale XCVU440。該元件是賽靈思利用3D堆疊式矽晶互連技術,將多個晶片並列堆疊在矽基板上,使每個晶片都連接在一起。

這種方法使賽靈思能夠在28製程上提供「大於摩爾定律」的容量,並利用具有1,954,560個邏輯單元的Virtex-7 2000T,實現創新世界紀錄的電晶體數量和FPGA邏輯單元容量。賽靈思的Virtex UltraScale XCVU440打破了原先保持的紀錄,提供可用於程式設計且具有440萬邏輯單元(相當於5000萬ASIC門)的20nm元件,內建超過200億個電晶體,成為至今為止世界上密度最高的IC。

Kirk Saban談到,我們期望具有該容量等級的元件能成為ASIC、ASSP以及系統模擬和原型設計的理想選擇。一些廠商專門開發用於ASIC原型設計的大規模商用基板,但有更多的公司則建構自己的原型設計系統。大部份的公司都在為原型設計找尋最高容量的FPGA。而Virtex-7 2000T元件可以說是在28奈米製程領域的領導者。

Ultrascale可實現CFP4的400G網路

Kirk Saba進一步談到,20奈米UltraScale產品系列,可為所有使用者提供新一代功能並協助開發出新一代Smarter系統(如圖3)。20奈米的 Kintex和Virtex產品線的特色尤其適合於網路、資料中心和無線通訊領域中的關鍵應用。

| 圖三 : UltraScale元件為新一代創新Smarter系統的理想選擇。 |

|

現今,網路領域正經歷100G應用的重大發展。Kirk Saba分析,前端系統已開始採用100G技術並快速地成為主流,同時擴展至相關週邊市場,使設備可連接到100G網路。與此同時,領先的網路用戶端已開始著手開發新一代400G和TB級設備。全新的UltraScale元件可支援開發100G解決方案及移轉至更先進400G技術的客戶。

賽靈思的第一代SSI技術,造就了Virtex-7 H580T元件,可用於創建CFP2光學模組的網路所需之2x100G晶片轉發器。而第二代SSI技術,可以用更出色的效能,協助客戶推出單FPGA轉發器線卡和CFP4光學模組。

Kirk Saba透露,對於希望遷移到CFP4模組並將400G設計放到單個FPGA元件的設計人員來說,選用UltraScale元件的理由如下,UltraScale有許多的32G收發器,可透過新一代晶片至晶片介面(CAUI4)做為連接到CFP4光學元件的介面。同樣重要的是能支援400G的頻寬,新一代佈線和類ASIC的時脈功能,可支援400G系統所需的大量資料流量。

此外,Kirk Saba還談到,Virtex UltraScale也可支援分數鎖相迴路(PLL),能減少設計所需的外部電壓控制振盪器的數量。他更談到,在UltraScale中可使用一個VCXO並在內部生成所需的任何其它頻率。這樣一來可以透過系統整合可降低物料清單成本和功耗,而這僅僅是來自線卡整合所帶來的成效,還不包括CFP4光學元件整合,可帶來的成本與功耗降低。

UltraScale可實現更低成本和功耗的NIC

隨著當前雲端運算應用的快速發展,IT部門需要為其資料中心選用更加精密、更低功耗和成本的運算資源。賽靈思Virtex-7 XT元件搭配整合x8 Gen3模塊,已成為大部分先進資料中心架構核心網路介面卡的核心元件。

對於網路介面卡(NIC)而言,PCI Express端的資料吞吐量(出口)必須與乙太網路端的資料吞吐量(入口)保持一致。Kirk Saba也談到,對於100G NIC而言,需要多個PCIeR Gen3整合模塊。在上一代產品中,Virtex-7 XT是唯一具有整合x8 Gen3模塊並滿足這些要求的元件。」

隨著UltraScale產品的推出,現可選用更低成本與功耗的Kintex UltraScale FPGA來滿足相同的性能要求。Kintex UltraScale具備多個PCI Express Gen3整合模塊及一個在7系列中屬於軟IP核的整合100G乙太網路MAC。

Kirk Saba指出,運用NIC於UltraScale Kintex可實現中階元件應用,而且還能釋放邏輯資源,實現額外且微分的封包處理功能。

UltraScale可實現無線通訊

在無線通訊設備產業,廠商正在同步推出LTE和LTE Advanced設備,同時,也著手開發更具前瞻性的應用。新系統勢必將以更加精密的架構問世,以實現多重發送、多重接收和波束成形功能。

Kirk Saba透露,LTE和LTE Advanced系統內的最新一代波束形成設備,普遍採用的架構使用兩個Virtex-7 X690T FPGA,客戶會這樣選擇是因為它同時具備充足的DSP和BRAM資源。Saban說,賽靈思現在可透過Kintex UltraScale產品,提供成本更低的單晶片完成相同的工作。

「Kintex Ultrascale系列提供高於中階元件所需的DSP模塊增加了40%。此外,它還包含預加器平方及其它累加器回饋路徑,這樣就能獲得更出色的DSP48的效率、方程式疊合及更高效的運算。這意味著雙晶片的UltraScale Virtex級應用,可簡化為48通道處理的單顆Kintex KU115應用。」

Kintex UltraScale KU115具有5,520個DSP模塊和2,160個BRAM,Kirk Saba對其評價甚高:它是業界最高的訊號處理能力,且比GPU強大。

此外,賽靈思的Vivado設計套件可搭配最佳的高層次綜合工具Vivado HLS。實現賽靈思對該工具進行了協同最佳化,幫助用戶有效地實現波束形成和其它需要大量的數學運算應用所需的複雜演算法。

(本文作者現為賽靈思Xcell雜誌發行人)