簡介

低電壓正發射極耦合邏輯 (LVPECL) 是一種既定的高頻差動訊號標準,此標準最早可回溯至 1970 年代以及更早的時期,當時高速 IC 技術僅侷限於 NPN 電晶體而已,由於僅能實現主動上拉,因此外部元件必須被動地將輸出下拉。對於直流電(DC)耦合低電壓正發射極耦合邏輯而言,這些外部元件不僅將輸出驅動器偏置至導通狀態,也終止了相關差動傳輸線。然而,對於首次使用 LVPECL 的使用者而言,在完成輸出級的設計時,此種可實現兩種需求的電路設計彈性,可能會是令他們混淆的來源。他們往往面臨到一系列的終端選項,並且沒有可據以做出選擇的基礎。

本文旨在透過系統化的方式來進行拓撲,以及做出元件規格值的選擇,將會以輸出驅動器的架構以及標準的供電電壓減 2 伏特 (VCC-2V) 的偏壓及終端線路來做為開端。這種終端的特性與限制將會被深入的討論,而且使用較少元件及較低功耗的替代線路 T 與 PI 終端,將會在此進行介紹及說明其特點。除此之外,有著內部終端的時脈接收器之使用,以及偏壓電組的選擇,以及供交流電終端所用之耦合電容,也都會在此一併討論。

LVPECL 驅動器

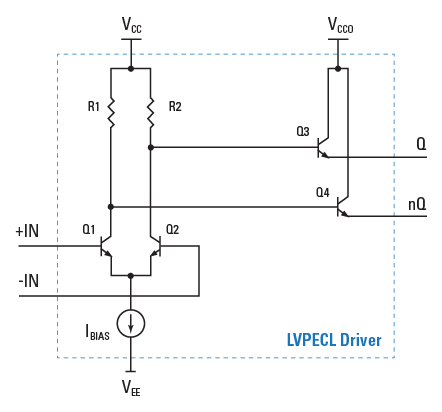

簡化的 LVPECL 閘通常是與開路發射極 (open emitter) 驅動器一起執行,如圖一所示。

| 圖一 : 開路發射極 (Open Emitter) LVPECL 驅動器的等效原理圖 |

|

在圖一中,可以明顯注意到三件事:

1) 輸出電晶體並沒有打開;因此這個驅動器將不會產生輸出。

a. 為了讓Q和nQ切換,每一個都必須以直流電路徑至接地的方式來載入。

b. 假如輸出未被使用,則 Q 以及 nQ 引腳可以浮接,以確保輸出是被關閉、並將功耗最小化及降低雜訊。

2) Q 以及 nQ 的發射極電流是由所選擇的外部下拉電阻所決定。這些不同規格值的電阻是根據不同的輸出電壓 (VCCO)、消耗功率以及 p-p 信號擺動 (signal swing) 而進行調整。

3) 輸出電壓 (VCCO) = 供電電壓 (VCC);不同於低電壓互補金屬氧化物半導體 (LVCMOS),VCCO 不可以低於 VCC,來遷就時脈接受器使用不同的供應電壓。舉例而言,VCC = 3.3V 以及 VCCO = 2.5V 將會導致輸出電晶體達到飽和,而大幅度地減少切換時間。

差動輸出的LVPECL 驅動器能夠在十億赫茲 (gigahertz) 的頻率下運作,該狀況是需要相關聯的低電壓正發射極耦合邏輯接收器透過適當的傳輸線來與驅動器連接。電路設計人員可以在元件布局的容易度,以及功率相對於效能的考量間來做取捨,以選擇終端,但是需透過包括導線長度與導通孔在內的模擬,去驗證信號的完整性。

直流電耦合的低電壓正發射極耦合邏輯 (LVPECL) 終端

標準式終端

下方圖二所顯示的就是標準式直流電耦合的LVPECL 終端。參考圖一,額定的 VTT 電壓是將克希荷夫電壓定律 (Kirchoff’s Voltage Law)應用至電路設定而成,此電路包含 VCC (=VCCO)、R1、Q4 及Rterm 的 Vbe,而這時 Q4 是在低電平邏輯 (logic low level) ,以及它的發射電流為 2 毫安培。VTT是一個支路電壓 (voltage branch),它被加在終端電阻的共同節點上,可同時滿克希荷夫電壓定律 (KVL) 及確保 VTT 電壓追蹤 VCC 與 VCCO 。VTT 的好處在於驅動器的輸出電流不會因為電源供應器電壓的變動而受到影響。這對於低電晶體邏輯 (logic low transistor) 電路而言是特別重要的,可以讓它保持在截止區 (cutoff) 之外,進而維持元件的切換速度。這個終端線路的明顯缺點則在於它需要一個參照於 VCCO的 -2 伏特穩壓器。

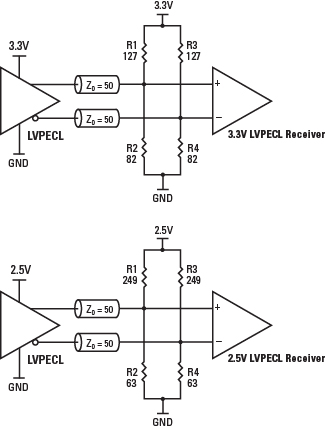

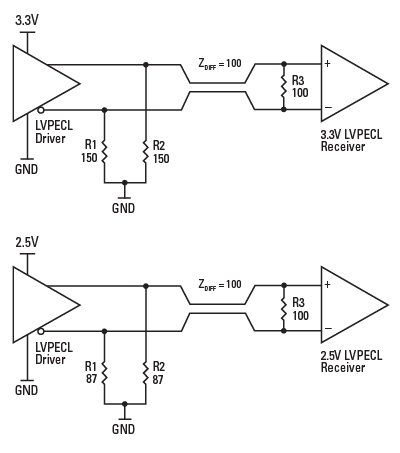

戴維寧(Thevinin) 等效終端

在實際應用上,VTT 所供應的電壓,經常被下方圖三中的終端所消除,在該終端中,每一個輸出的 VTT 電壓與 50 歐姆的終端電阻,皆由兩個電阻偏壓串 (resistor bias strings) 的戴維寧等效電路所同時實現。Q 與 nQ 單獨分開的終端,可以讓 Q 與 nQ 在無耦合的傳輸線上,有著被路由至不同單端負載 (single ended loads) 的選項。

| 圖三 : 3.3V 以及 2.5V 的戴維寧 (Thevinin) 等效LVPECL 終端 |

|

戴維寧 (Thevinin) 終端有五個缺點:

1) 偏壓串 (bias string) 除了輸出驅動器發射極電流之外,還會產生自己本身的功率代價 (power penalty),這個功率代價在 3.3 伏特的供應電壓時,每個輸出對 (output pair) 大約是 80 毫瓦。

2) 在終端並無餘裕可適應 VCCO、溫度以及元件製程上的變化。

3) VCCO 上的變異部分,會被偏置電壓分壓器 (bias voltage divider) 前饋 (fed forward) 至戴維寧 (Thevinin) 等效 VTT 電壓上; VCCO=3.3 伏特時,是 39% ; VCCO=2.5 伏特時,是 20%。因此,特別是對於低輸出邏輯電路而言,發射極電流的控制不如同標準 VTT 終端那般有效率。

4) 對於差動終端 (differential termination) 而言,真正需要的僅有三顆電阻,即可實現一個 VTT 電壓,以及兩個 50 歐姆的終端阻抗。

5) 對於每一個 Q 與 nQ 信號而言,連結至時脈接收器端點上的兩顆電阻,會因為在單一電阻上產生額外的寄生電容,而增加了線路佈局的複雜度以及效能損失 (performance penalt)。

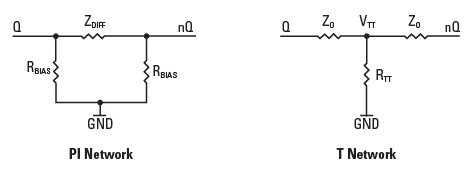

PI 型與 T 型分流終端

若要避開壞減少戴維寧終端的缺點,可以使用如圖四所示、由 PI 型(也稱為 Delta 型)或是 T 型(也稱為 Y 型)的電阻線路所組成的耦合傳輸線。PI 型線路的共模阻抗是 Rbias/2, T 型線路則是 Zo/2+RTT。供給PI 型線路之耦合傳輸線的終端阻抗是 Zdiff,它等於 2*Zo;而供給T 型線路的則直接是 2*Zo。跨越 RTT 的共模電壓,由於類似於 VTT=VCC-2.0V 而被命名為 VTT。

| 圖四 : T 型與 PI 型LVPECL 終端線路 |

|

這兩種線路可解決戴維寧終端的缺點,如下所述:

1. 由於其終端是由驅動器電流所直接供電,因此可消除戴維寧偏壓串的功率代價。

2. 這個共模阻抗,以及因此而產生的負回饋,可以依據下表一所顯示之VCCO、溫度以及元件製程情況的不同,而予以調節,來平衡驅動器的電流。

3. 這種 PI 型以及 T 型線路透過共模電流的回饋,可以對發射極電流有著較好的控制。以 RTT = 50 歐姆以及 VCCO = 3.3 伏特的 T 型線路為例,從 VCCO 到 VTT 節點的共模回饋為 66% (事實上,因為是在輸出電晶體的不同運作點,因此會稍微差了一些),這相較於標準式終端的前饋路徑高了 60%。然而介於這兩種終端之間的差異性,起初似乎並不顯著,而當低電晶體邏輯電路的50 歐姆發射極電阻出現小幅電壓下降時,它就會變得顯著。

4. 在最低條件下,僅需要三顆電阻即可偏置這兩個輸出並且終止傳輸線。對每一個線路而言,Q 以及 nQ 傳輸線必須耦合在一起,因為每一個線路都實現了一個分流終端。

5. 在這種LVPECL 接收器的每一個輸入終端上,僅需要放置一個電阻端點,以及因此而產生的相關寄生電容即可。

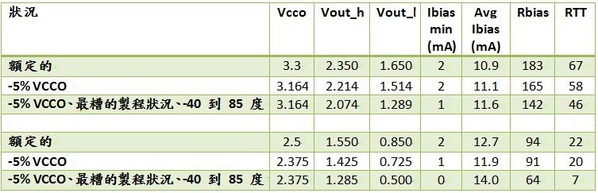

表一、顯示出 PI 型與 T 型終端的共模偏壓電組是如何被調節以適應 VCCO 與元件製程中的變異。IDT 853S006 被視為代表性元件,該元件的LVPECL 輸出的特點,在於能在整個工業溫度範圍內提供最大與最小的邏輯 0 與 邏輯 1 電壓。針對三種情況進行計算;額定 VCCO 電壓;極端狀況下的 -5% VCCO 與整個製程及溫度範圍內的最小共模輸出電壓;以及適中狀況下僅 -5% VCCO。

| 表一 : 輸出電晶體電流 vs. T 型與 PI 型終端的偏壓電阻 |

|

在期望的切換速度下,低電平邏輯電路的最小偏壓電流會相對應減少,來補償在兩種 -5% VCCO 狀況下逐漸降低的機率。隨著發射極電壓所帶來的變化越來越大,偏壓電阻必須減少來適應輸出電晶體發射極電壓的逐漸降低。減少偏壓電阻時,也會增加平均的偏壓電流。要應付這樣的情況,不出所料就是得減少最小的 Ibias、降低平均的偏壓電流。比較 2.5 伏特的 VCCO 偏壓電流與額定及 -5% 狀況,很明顯就能看到這種效果。

差動對 (differential pair) 的平均偏壓電流,是根據每個情況使用的 VCCO 計算而來。在所有情況中,當 VCCO 是 +5% 時,偏壓電流將會增加。設計人員應該根據情況條件,選擇能最佳因應其應用誤差的電阻值。

PI 型終端與耦合傳輸線

當你將圖四中的 PI 型線路與耦合傳輸線合併時,Zdiff 會被終止於 Zdiff 的耦合傳輸線等效阻抗所取代。這樣的佈局保留了使用 Rbias 來獨立設定 Q 與 nQ 偏壓電流,以及每個接收器端點僅需要一個寄生電阻即可的優勢。下方圖五顯示具體的 PI 型線路。

若是將多重LVPECL 信號終止於球閘陣列封裝 (BGA) 此類單一封裝電路板上,針對這種佈局,這種終端是最有利的方式。事實上,這樣的優勢就如同接收器是由低電壓差動訊號 (LVDS) 所提供一般。Q 與 nQ 輸出在每個傳輸線上僅有一個 Rbias 電阻,如此一來可使其容易被佈局與LVPECL 驅動器在電路板上的同一側,因此可以提供顯著的信號整合優勢。

在某些元件中,LVPECL 在輸入階段,以共模封裝 (tap) 整合了 50 歐姆的差動終端電阻,並引出至封裝引腳,這通常會標示為 VT。當執行 PI 型終端時,VT 端點是浮動的。

| 圖五 : 3.3 伏特與 2.5 伏特的外部 PI 型終端 |

|

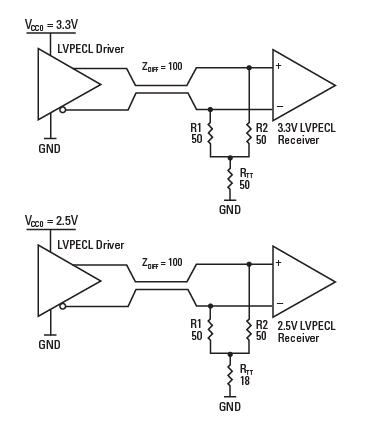

T 型終端與耦合傳輸線

當你將圖四中的 T 型線路與耦合傳輸線合併時,整個 T 型線路是被佈局在耦合傳輸線的LVPECL 接收器那端。這時每個接收器端點僅需一個寄生電阻,而且與 RTT 關聯的寄生電容,因為它是位於 VTT 共模節點,因此並不會影響到差模 (differential mode) 信號的完整性,於是 T 型終端成為大型扇出的LVPECL 元件的首選,舉例而言,在時脈接收器中,一個 1:22 的扇出緩衝可能很難容納 PI 型終端所有的下拉偏壓電阻。

下方圖六顯示特定形式的 T 型線路。對於一個整合了 50 歐姆的差動終端電阻以及共模 VT 封裝的LVPECL 元件而言,這些範例所顯示的 VT 引腳,是穿過外部的 RTT 電阻而拉到接地點。

| 圖六 : 3.3 伏特與 2.5 伏特的外部 T 型終端 |

|

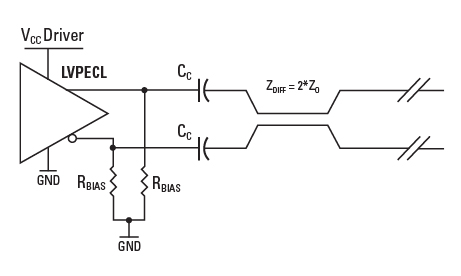

交流電耦合終端的低電壓正發射極耦合邏輯 (LVPECL) 偏壓

通常LVPECL的時脈驅動器,必須與具有不同切換臨界電壓 (switching threshold voltage) 的各種邏輯電路系列接收器,以交流電耦合在一起,這個LVPECL的輸出必須仍然是偏壓直流電,但是阻擋電容 (blocking capacitors) 的使用,會在它的共模範圍內加上所需求的條件來偏置接收器,並且在LVPECL 的接收器上提供傳輸線終端阻抗。在圖七中所顯示的是僅供給LVPECL 驅動器的一般外部配置。

| 圖七 : 交流電耦合負載的一般LVPECL 驅動器偏壓 |

|

表一提供Rbias 電阻的規格值;該表數據是根據將輸出電晶體發射極電流設定在切換臨界值上所計算而得到的。Cc 的規格值是根據時脈的頻率以及時脈頻率上的阻抗大小所計算而得。

耦合電容的選擇是根據該上限被允許導入至信號路徑中的寄生電抗 (parasitic reactance) 數量而定。為了計算

表二(顯示在下方)關聯標準的上限值,以及它們相對應的頻率範圍,這個最大的阻抗是任意設定於 0.2 歐姆。

結論

LVPECL 是一項較老舊的技術,它可回溯至當半導體製程尚未成熟至高效能 P 型元件可以與高效能 N 型元件一起製造的年代。因此之故,P 型元件的角色必須以外部的被動元件來處理。這項條件被運用在LVPECL 上,而且也藉由將被動式下拉功能的角色與傳輸線終端合併,來運用在LVPECL 的前身,亦即發射極耦合邏輯 (ECL) 上。

設計人員通常難以設計出合適的LVPECL 終端,這是因為在完成輸出級設計時,他們一般不會去檢視終端的角色。之所以從電路角度來呈現LVPECL 終端,其目的在於展現這些重要因素,包括輸出電晶體電流、最小化零件數量及功率等,對於LVPECL 終端的拓撲以及一般終端的零件數值而言是多麼重要。現代的半導體製程已可生產高效能 P 型元件,所實現的電路是接地參考差動信號系列,例如主時脈信令等級 (HCSL) 以及低電壓差動訊號 (LVDS)。這些系列可完全消除 對於VTT 的需求。

作者:Phillip Wissell

職稱:資深應用工程師

Integrated Device Technology 公司

時序暨同步化部門