在軍事以及航太環境中,某個團隊可能會需要空運連結機組、衛星通訊、一個基地中繼站、以及一組緊急發射器,再加上特定應用所需要的裝置,像是UAV(無人機)作業等,彼此不同而且不相容的無線電激增是一項嚴重的問題。這些無線電的連結都各自具備其重要的目的,將任一項排除在外都會使作業中的團隊失常。然而每種無線電無疑地會在成本、重量、以及備用電池需求方面增加成本。而當新的需求與連結加入之後,問題將會更加的複雜。

解決方案顯而易見,至少在”文件”上是如此:採用可以使用於所有平台,而且能夠在現場依照需求動態性重新配置的通用型全雙工無線電模組。”單一無線電”的目標將可以減輕其負擔、提供彈性與多功能性,同時更具效率以延長單組電池的運作時間,進而獲得顯著的SWaP(尺寸、重量、電力)優勢。而那就是JTRS(聯合戰術無線電系統)以及軟體定義無線電(SDR)之類計劃的基本前提。

但是要將”通用”無線電概念加以實現,其實遠比想像還要來得困難許多。雖然摩爾定律(Moore’s law)已經讓必須要具備的高性能、低功率處理器(包含FPGA在內)獲得了實現,但是要提供適用的整合型類比前端(AFE)卻變得更加的困難。此類型功能區塊-設置於天線與處理器之間,同時也是真實信號世界與數位世界間的介面-的要求非常的複雜、多變而且嚴苛。

一直到最近才有一款實際的類比前端適用於此類多功能無線電所需的重疊式平行通道陣列,每組都被設計成可以涵蓋特定區段的RF頻譜,並且具備了足以匹配所需信號格式的頻寬。這種方案雖然可行,但是在最終的PC電路板基底尺寸、重量、電力上卻需要耗費大量成本。

高性能單晶片類比前端解決方案

幸好,目前已經有一款新的RF IC能夠因應充滿挑戰性的軟體無線電需求,並且可以使軟體無線電的概念朝實現的目標更往前邁進。來自於ADI的AD 9361 RF(射頻)捷變收發器是一款寬頻、可編程的前端,支援雙工獨立收發器通道,能夠做為快速成長中的多重輸入、多重輸出(MIMO)區塊以及非MIMO的需求。系統處理器可以針對關鍵參數(像是頻寬與RF頻率等)動態化的重新配置,以便符合應用裝置的需求,並進而提供最佳化的結果。該元件也具備了能夠支援頻率捷變通訊協定的特點。

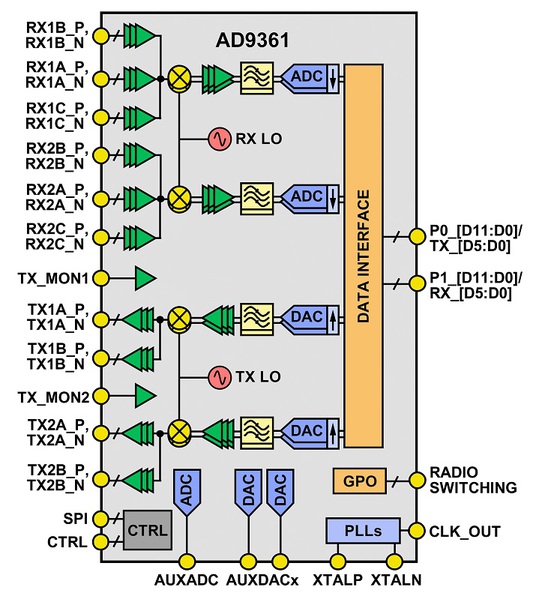

這款10 x 10 mm晶片等級的元件,如圖1所示,具備了200 kHz 至56 MHz的使用者可調整頻寬,以及其它在建構橫跨70 MHz 至6 GHz信號鏈時所需要的特點與效能屬性。使用這款2 x 2直接轉換元件可以將整個類比前端縮小至一個單一而且相對簡單的電路當中。該元件透過LVDS或是CMOS埠與主要處理器連結,藉以增加速度與簡化性。該元件內建了12位元A/D與D/A轉換器、分數N型合成器、數位和類比濾波器、AGC(自動增益控制)、發射功率監測功能、正交校正、以及其它重要的功能。

該元件除了高整合性之外,其RF、類比以及混合信號性能都非常的優秀。舉例來說,接收器雜訊係數低於2.5 dB,而發射器EVM(誤差向量振幅)優於- 40 dB,發射器雜訊層則低於- 157 dBm/Hz。在發射與接收路徑方面,為了可以進行精密的調節,本地振盪器的步進大小只有2.5 Hz。雖然該元件內建了許多的功能,但是功率消耗一般都只有1 W而已。

| 圖一 : ADI的AD 9361是一款2 x 2的直接轉換收發器IC,具有70 MHz 至6 GHz的涵蓋範圍,提供從200 kHz到56 MHz的使用者可調整頻寬,以及12位元轉換器解析度。 |

|

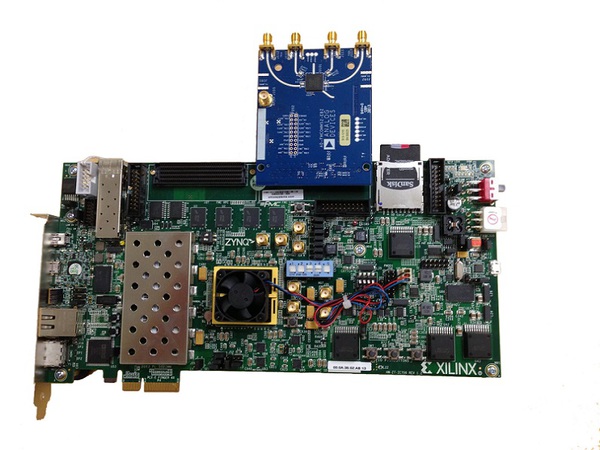

超越IC的系統設計

由於彈性化的寬頻SDR這類型的複雜設計牽涉到主要的電路設計投入,以及演算法的開發與權衡,因此AD 9361提供一款搭配Xilinx (賽靈思公司)FPGA使用達到最佳化的參考設計。ADI的AD -FMCOMMS2 -EBZ FMC板(FPGA夾層卡)透過單一FMC連結器連結至Xilinx主要電路板,藉以提供能夠支援AD 9361在2 x 2通道配置下所需要的電力與頻寬,如圖2所示。該電路板在軟體方面可以完全客製化,不需要在硬體方面做改變,同時能夠針對不同的MIMO配置提供額外的選項。

該參考設計包括電路圖、電路佈局、物料表、HDL、Linux驅動程式、以及應用軟體等所有在驗證性能與快速的系統原型建構時所需要的關鍵細節。除了較低階的軟體與韌體之外,使用者擁有利用Simulink以及MATlab支援的能力,這將可以實現無線電演算法與性能的程式碼開發與調整。

| 圖二 : 系統開發者能夠以Xilinx FPGA使用AD 9361 FMC板進行開發、除錯、評估、以及調整他們的SDR應用裝置-以最少的硬體設定。 |

|

可能…比你能夠做的還要更好

由於這款小巧、高性能以及彈性化的IC能夠取代大量的分離式電路,因此這些分離式設計的需求似乎就應該要功成身退了。但其實不盡然如此,因為一個針對SDR全範圍的特定區塊、格式與頻寬加以良好設計、謹慎除錯以及適當佈局的分離式類比前端設計,儘管會具有較大的佔位面積,卻可能會在該特定區塊超越AD 9361 IC。

但是真正的挑戰在於SDR中類比前端的極端寬頻性質,這需要許多像這樣的頻譜特定前端,而每一個前端對於設計與評估都是一項巨大的挑戰,使得最終的產品會遠遠的落於SwaP排名之外。因此,在權衡取捨方面就會更傾向於AD 9361 IC,因這顆IC具有足以因應大部分情況的充足RF性能,而且缺點也遠遠少了許多。

ADI的AD 9361 RF捷變收發器不僅只是另一款受到高度期望與樂觀的技術手冊所支援的”即將問世”IC而已。該元件是真實的,FMC板與工具也是真實的,而且已經被採用到兩款已問市的SDR產品中:分別是Ettus Research的 萬用軟體無線電週邊(Software Radio Peripheral; USRP) 以及由Epiq Solutions 開發的Maveriq 多通道可重配置式RF 收發器。

不論系統工程師是比較喜歡利用ADI FMC進行他們的SDR設計與開發,或是以現有的商業用SDR作為平台,以AD 9361為基礎的總體產品封裝與性能都能夠為他們帶來較多的優勢。

關於作者

Duncan Bosworth是ADI公司航太與國防部門行銷工程師。他主要任職於ADI美國威爾明頓廠。