隨著2013年的經濟景氣可望較2012年復甦,半導體市場亦有回甦景象。位居全球領導地位之晶圓製造業者除公布2013年第一季經營狀況之外,亦紛紛發表未來的資本支出規劃和先進製程提升藍圖。

尤其在2013年下半年,晶圓代工業者除可望加入20nm量產行列以外,亦紛紛公開14/16nm發展進程,甚至於推進至10nm。讓TSMC和GlobalFoundries得以追上以往難以企及的龍頭廠商Intel,而不至於始終落後一至二個製程世代。

本文即試圖從晶圓代工業者在邏輯製程的發展上著手,試圖剖析主要業者的發展動態,進而評析其背後原因和可見影響。

領導大廠紛紛宣告邏輯製程推進時程

TSMC於2013年第一季法說會中公佈將於2013年下半年進入20nm製程量產,並可望於2014年下半年量產16nm製程,但至2016年才可能量產10nm。GlobalFoundries亦來台宣告將在2013年下半年量產20nm,2014年下半年量產14nm,甚至預期在2015年即可提供10nm量產服務。

然而,根據Intel長久以來的Tick-Tock技術發展策略,即讓晶圓製程技術和處理器微架構進行交替更新,說明晶圓技術約兩年提升一個世代。向來居微處理器和邏輯晶片製程領先地位之Intel,恐怕會在GlobalFoundries和TSMC企圖以一年更新晶圓製程之競爭之下,在10nm世代被超越或趕上。

原本Intel以超越ITRS(International Technology Roadmap for Semiconductors)技術藍圖之速度發展晶圓製程,但近來發展卻呈現後進者快速發展之態勢,本文即試圖分析其緣由與影響。

製程發展加速產業競爭 競逐高階訂單

邏輯晶片晶圓製程提升水準正在加速

Intel繼2012年領先全球採用22nm之魚鰭式場效應電晶體(FinFET)技術量產處理器之後,預期將在2013年底推出14nm技術之處理器晶片,如下圖所示,仍依循兩年一個製程世代轉換之發展路徑。照此估算,Intel預期於2015/2016年間推出且量產採用10nm製程之處理器產品。

TSMC則領先晶圓代工同業在2011年推出28nm代工製程,並在2012年獲取IC設計業者28nm代工訂單,達到大幅成長。未來,預期在2013年下半年進行20nm製程量產,並規劃在2014年下半年量產16nm製程。

GlobalFoundries則於2012年下半年輔量產28nm,2013年下半年能否順利量產20nm尚不可知,隨即將於明年推進至14nm、後年至10nm,其技術之推進速度超越Intel、TSMC。但能否獲得上游材料、設備業者和其IC設計業者之研發支援,將是影響其規劃能否成功之關鍵因素。

至於UMC、SMIC和Samsung除了在28/32nm有較明確的規劃以外,近來在20nm或更先進製程尚未有明確時程。

資本支出仍影響邏輯晶片晶圓製程提升速度

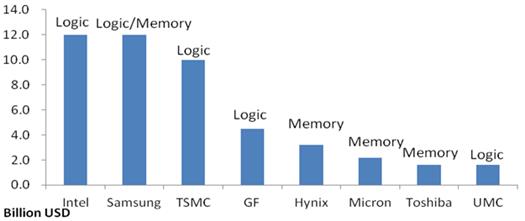

近日以來,Intel法說會已決議將2013年資本支出自130億美元下修至120億美元,與Samsung規模相當(Samsung亦包含記憶體產品);TSMC則從90億美元提高至100億美元,GlobalFoundries自35億美元提高至45億美元,如下圖所示。

| 圖一 : 主要晶圓製造業者之2013年半導體資本支出規劃 資料來源:資策會MIC |

|

Intel自中國大連廠之後並無大型擴產規劃,其資本支出多數用於技術發展和製程更新。TSMC則表示九成資本支出將用於先進製程之更新與擴產,此外亦規劃興建Fab16新廠。

GlobalFoundries繼美國紐約州廠逐漸加大量產規模後,亦無大型建廠規劃,可望將多數資本支出運用於製程提升,但其在先進邏輯晶圓製程投入規模恐仍與Intel、TSMC有所差距。

由於資本支出多寡攸關與上游材料、設備業者的合作關係,再者先進製程開發亦須有IC設計業者配合投入前期研發,因此並非單靠晶圓製造業者即可獨立完成製程水準提升。而不論就上游供應關係或下游客戶合作來看,GlobalFoundries尚不足與Intel、TSMC相抗衡。

新舊晶圓技術混用加速製程水準提升

近年來,由於邏輯晶片製程水準自45奈米之後逐漸出現技術瓶頸,難以大幅提升。目前雖仰賴浸潤式技術和Double Pattering、Multi Patterning等雙重、多重圖案技術,突破193nm曝光技術下之物理瓶頸,然而突破難度日益提高。

因此,面對20nm以下之更先進製程,促使晶圓業者企圖採用新舊製程技術混合方式以求突破,即是在原本極端複雜的邏輯晶片電路設計和晶圓製程之中,針對部分步驟率先導入14/16nm先進製程,其餘步驟則採用較為成熟之20/28nm製程,形成新舊製程技術混用之發展,以加速先進製程轉換速度,而未來10nm亦恐須採用同樣策略使能率先獲致成功。

然而,採用新舊混合製程,若14/16nm製程部分所佔比例不大或應用有限,則對整體晶片效能提升貢獻不大,再加上將大幅提高研發投入和製造成本,能否讓IC設計業者等客戶接受並開始大量量產,仍是未知之數。

提高資本支出 搶攻客戶高階訂單

未來可預見Intel、TSMC和GlobalFoundries率先推出14/16nm次世代邏輯晶圓製程,隨後有Samsung、UMC和SMIC等業者,能提供此類先進製程的晶圓製造者屈指可數。

然而相對來看,IC業者採用更先進製程亦須同時投入鉅額支出以進行合作研發須具備高出貨量的經濟規模,如Qualcomm、Broadcom和MediaTek等業者;或具高單價的特定產品,如Altera和Xilinx等FPGA業者,方能承擔鉅額共同研發投資。

因此,Intel即以其14nm FinFET技術拉攏與其業務關聯性低之FPGA業者Altera,TSMC和GlobalFoundries亦先後與ARM發表採用14/16nm最先進製程之處理器產品設計。上述業者動作,無非是希冀吸引IC設計業者與其合作開發。

結論

由於半導體市場規模成長幅度逐年趨緩,主流晶圓製程產能充裕且技術成熟,使得其晶圓產值或代工單價面臨下滑,進而衝擊到毛利率和營利。

因此,投入更先進製程以獲得較高的領先利潤,進而得以支撐未來的研發負擔,即是Intel和TSMC等領先族群的首要戰略,亦是目前GlobalFoundries亟欲進入領先族群的緣由。

然而高投資恐怕無法保障相應的報酬,尤其GlobalFoundires在面臨Intel和TSMC兩大巨頭的競爭之下,又恐怕會面臨同為IBM技術聯盟之Samsung爭食共同的金字塔尖端市場。

換個方向來看,縮減投資規模、加強主流製程、進而提升營運效能為UMC等業者的主要戰略,雖無法獲得高報酬利潤,卻也可以在目前製程發展激流之中站在較堅硬的磐石之上。

(本文作者潘建光為資策會MIC資深產業分析師)