採用矽穿孔(TSV)的2.5D或3D IC技術,由於具備更佳的頻寬與功耗優勢,並能以更高整合度突破製程微縮已趨近極限的挑戰,是近年來半導體產業的重要發展方向。在產業界的積極推動下,3D IC已從概念逐漸成為事實,預計將於二至三年後進入量產階段,必將成為未來市場的重要遊戲改變者。

TSV 3DIC市場逐步起飛

在日前舉行的Cadence使用者會議(CDN Live)與Semicon Taiwan活動上,包括台積電、聯電、日月光、Xilinx等大廠都釋出了表示3D IC即將邁入量產的訊息。

其中,積極以自有CoWoS技術搶市的台積電預計在今年十月就將發布1.0版的設計套件與PDK,試產時程訂於今年第四季,明年第四季可望開始正式投產。台積電更以今年將是台積電3D IC製造元年,來宣告此技術已獲得重大進展。

日月光集團總經理暨研發長唐和明則表示,高階產品朝2.5D/3D IC移轉已勢在必行,過去幾年來,此技術在IC設計、晶圓、封測等各領域均有顯著進展,預計量產時程為2014~2015年,應用將逐步興起。

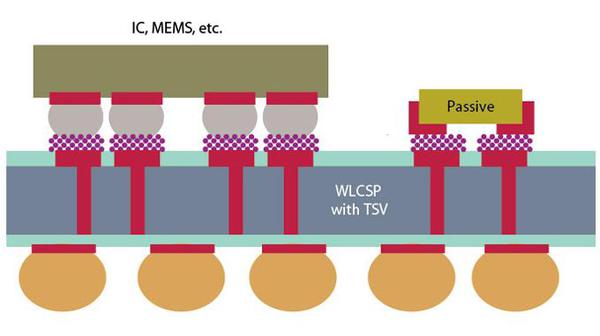

| 圖一 : 隨著3D異質堆疊技術的成熟,將使半導體產業打破摩爾定律的制約,開創出更寬廣的創新應用與技術。 |

|

聯電是以Via-middle製程為基礎,從今年初開始進行TSV製程最佳化,預計今年底便可進行產品級的封裝與測試以及可靠性評估。

而已經率先發表2.5D FPGA技術的Xilinx,該公司資深副總湯立人也表示,這款在單一封裝中整合4顆28奈米FPGA、總電晶體數高達68億個的元件,預計明年上半年就可正式量產。

從這些一線大廠的動態,我們可以看出,3D IC時代的確即將來臨!

3D IC在行動市場深具潛力

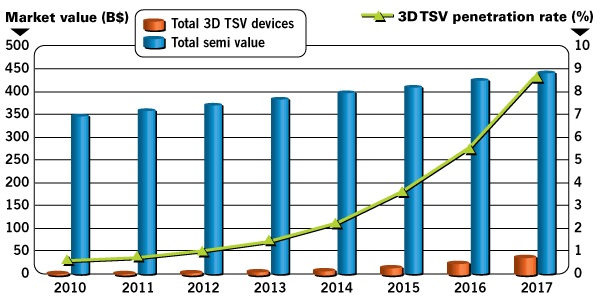

根據市場研究機構Yole Development發佈的數據,全球3D TSV晶片市場規模將從2011年的27億美元,到2017年成長至380億美元(不包含2.5D),佔整體市場的9%。目前的產值主要是來自低階的CMOS感測器、MEMS等應用,仍以8吋3D晶圓封裝為主,尚未移轉至12吋。

Yole Development估計,2017年全球3D TSV半導體的封裝和測試市場將達到80億美元,其中約有38億美元是與TSV蝕刻、填充、接線、凸塊、測試等中段製程業務相關。而後段的3DIC模組測試業務也將會達到46億美元,是封測廠商未來重要的成長契機。

目前,採用2.5D技術的FPGA元件已經朝向商業化,而在美光、三星、海力士等各家廠商的積極推動下,異質記憶體堆疊可望將於伺服器和高效能運算(HPC)市場率先導入,Yole Development認為明年將會是3DIC真正大量應用起飛的開始。

3D IC的真正重點在於將記憶體與邏輯IC堆疊在一起,以取得更佳的效能、尺寸、以及功率優勢,這塊領域將是未來五年3DIC市場最重要的推動力量。不過,業界矚目的TSV 28奈米行動應用處理器,可能要到2014至2015年才會在wide I/O介面廣泛採用後,而開始有大量應用。

有鑑於行動市場的強勁成長動能,這也是台積電和三星積極搶奪市場的首要戰場,希望透過整合從前端製造到後端封測的垂直式整合作業方式,以滿足高通、NVIDIA、Broadcom等一線晶片設計業者的需求。

在Semicon Taiwan的3D IC論壇中,有與會來賓透露,三星明年的智慧型手機就將搭載採用TSV技術的3D IC,能以其集團的垂直整合優勢,帶來更佳的系統效能表現。

不過,即使技術陸續到位,但目前整體供應鏈還是非常分散,需進一步的整合,同時到底未來何種3DIC的業務模式會勝出,態勢也尚未明朗。產業生態系統還需要一段時間的發展,才會更臻成熟。

業務模式之爭 仍未明朗

看好3DIC市場的發展前景,晶圓廠和封測業者均加碼投入,同時依via-first/via-middle/via-last不同的TSV製程技術,出現了多種不同的業務模式。

像台積電的CoWoS技術,強調一條龍式的製程,提供從前端到後端的完整服務,而聯電的via-middle技術,則是藉由與封測廠的夥伴關係,共同提供服務。

這兩種模式,就技術、服務效率來看,各有其優缺點。站在無晶圓設計業者的立場,via-last能帶來更佳的供應鏈管理靈活性,不會被單一業者綁住,也能有更多元的方案可選擇。但另一方面,在晶片品管、責任歸屬方面,有可能會造成更多的困擾。

Yole Development則認為,採用「via-middle」模式的記憶體和邏輯IC堆疊將成長最快。

日月光研發中心副總經理洪志斌也指出,以目前的2.5D中間插件(interposer)供應為例,就有晶圓代工、封測廠、結合兩者,以及獨立供應商的不同業務模式。晶片客戶也會在不同的業務模式間移轉,並沒有明確的主流態勢出現。

這些都是產業鏈在朝成熟發展過程中,尚待克服的問題,包括生態系統、合作關係、競爭模式都還在摸索階段。此外,目前3D IC的成本仍高,有賴共通標準、代工廠間互通性的建立,才有可能以更佳的成本效益與效能,推動更廣泛的採用。而在技術成熟度方面,眾所矚目的3D IC異質堆疊在微凸塊/TSV、熱傳、TSV元件應力、3D製程開發套件、晶片間介面、測試等各個領域也都還待解決。

儘管挑戰仍在,但我們看到了3D IC技術的顯著進展,已經從概念成為可行的商業化產品。未來,隨著3D異質堆疊技術的成熟,將能使半導體產業完全打破摩爾定律的制約,反而可以開創出更寬廣的創新應用與技術,這樣的前景的確令人期待。

| 圖二 : 3D TSV元件佔半導體市場比例將於2017年達到9%,規模為380億美元。資料來源:Yole Development, 2012/7 |

|

力抗三星 台積電晶圓、封測一手抓

為抗拒三星和Intel跨足晶圓代工的競爭,以及從三星手上搶下蘋果處理器(A7)的訂單,台積電近年來跨業整合的策略明確,從入股Mapper、ASML等半導體設備商,轉投資創意電子,擴大晶圓代工事業,到佈建逾400人的封測團隊,不斷出手進行一條龍事業體的布局。

事實上,跨業整合已是台積電維持龍頭地位不得不走的路,因為下一個半導體業競賽的技術已非對晶片集積度進化的追逐,比得是誰能最有效率且最有彈性地實現3D IC產品。目前,三星在這個領域站在領先地位,據分析也是台積電無法吃下蘋果A6晶片的主因之一。

由於3D IC橫跨晶圓及封測業兩端,因而衍生出via-first/via-middle/via-last等不同的TSV製程技術,以及多種不同的業務模式。不過,透過整合從前端製造到後端封測的垂直式整合作業方式,已是三星和台積電很清楚要走的路。

針對3D IC,台積電端出的菜稱為CoWoS(Chip on Wafer on Substrate),就是將邏輯晶片和DRAM放在矽中介層(interposer)上面,然後封裝在基板上,這個架構屬於2.5D IC封裝架構。對於台積電跨足到封測領域,負責「CoWoS」製程研發的台積電資深處長余振華曾經指出:「最重要的理由是,封測業已經跟不上晶圓代工的腳步了。」

余振華這麼說的理由,除了3D IC必須跨領域設計外,對於先進製程的良率控制上,晶圓與封測分家的生產體系,容易造成責任不易釐清的問題。因此希望透過一條龍的服務方式來擔起所有的風險,也能滿足Apple這個潛在大客戶及現有主力客戶包括Xilinx、AMD、NVIDIA、Qualcomm、TI、Marvel、Altera等對2.5D IC的迫切需求。

當然,台積電此舉也對日月光、矽品及力成等一線封測廠造成很大的壓力。為了力掃市場對封測業將流失地盤的說法,日月光及矽品皆強調,在先進高階封測製造不會缺席;力成則決定捨棄2.5D直接跨入3D IC,率先導入應用在記憶體DRAM產品。(CTIMES科技日報)