什麼是閉鎖狀況?

閉鎖可以定義為由於觸發了一個寄生元件而在電源供應軌之間建立了一個低阻抗的路徑。閉鎖會發生在CMOS元件當中:當兩組寄生的基射介面(base-emitter junctions)其中之一發生了暫時性的正向偏壓時,來自於PNPN SCR結構的原生寄生元件(圖12)。SCR會開啟,進而在供電之間造成持續的短路。觸發了閉鎖狀況是很嚴重的:在最好的情況下,它會導致元件機能失常,藉由必要的功率循環使元件恢復正常運作;在最糟的情況下,假如電流流動未受到限制的話,元件(甚至包括電源供應)可能會損毀。

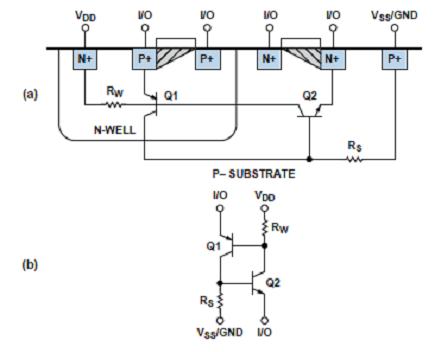

| 圖十二 : 寄生SCR結構:(a)元件(b)等效電路 |

|

前面所提到的故障以及過電壓狀況都屬於觸發閉鎖狀況的常見原因。假如在類比或是數位輸入上的信號超過了供電,那麼寄生電晶體就會開啟。這個電晶體的集極(collector)電流會導致電壓位降至第二寄生電晶體的基極-射極,進而將電晶體開啟,產生出在供電之間的自我維持路徑。圖12(b)中清楚的展示了在Q1與Q2之間所形成的SCR電路結構。

觸發閉鎖狀況的事件不需要持續很久。短時間出現的暫態、峰值、或是ESD事件就可能足以使一個元件進入閉鎖狀態。

當供電電壓被壓迫至超過該元件的絕對最大額定值,導致內部接點斷開與SCR被觸發時,閉鎖狀況也可能會發生。

假如供電電壓被提高到足以使內部接點斷開,進而阻止電流流入SCR的話,第二種觸發機制就會發生。

處理閉鎖狀況的最佳方法為何?

對抗閉鎖的保護方法包括了在對付過電壓狀況時所建議的相同保護方法。在信號路徑中增加限制電流的電阻,在供電上增加蕭特基二極體,以及將二極體與供電串聯(如同圖8與圖9中所示),這些都有助於避免電流流入寄生電晶體,進而也避免了SCR被觸發。

具有多重供電的開關可能會有違反絕對最大額定值的額外電源供應定序問題。不適當的供電定序可能會導致內部二極體的開啟,並且觸發閉鎖狀況。連結在供電之間的外部蕭特基二極體會在多重供電加諸於開關時,確保VDD一直都在這些供電的二極體位降(對於蕭特基為0.3 V)之內,進而適當的避免SCR傳導,也因此免於違反最大額定值。

目前有提供什麼樣的預封裝解決方案?

做為使用外部保護功能的替代性方案,有些ICs會利用具有外延層(epitaxial layer)的製程進行生產,這可以提高SCR結構當中的基底電阻與N型井電阻。越高的電阻所代表的是觸發SCR需要更嚴苛的應力,進而導致元件對於閉鎖會較不敏感。有一個範例就是ADI的iCMOS製程,以其所生產的ADG 121x、ADG 141x、以及ADG 161x開關/多工器家族。

對於需要閉鎖保證解決方案的應用裝置而言,目前的溝槽隔離式開關與多工器保證能夠在以±20 V運作的高電壓工業應用裝置中實現閉鎖的預防。ADG 541x以及ADG 521x家族乃是針對儀器、汽車、航空電子、與其它容易造成閉鎖的嚴苛環境所設計。其製程是在每個CMOS開關的N通道與P通道電晶體之間設置絕緣氧化層(溝槽)。水平與垂直的氧化層會在元件之間形成完整的隔離。在接點隔離式開關中電晶體之間的寄生接點會被消除掉,進而產生出完整的閉鎖保證開關。

工業上的慣例是將輸入與輸出對於閉鎖的敏感度予以分級,其分級的依據為:在內部寄生電阻發展出足夠的電壓位降以便維持閉鎖狀況之前,I/O接腳在過電壓情況下所能夠流出或流入超量的電流量。

100mA通常被認為是適當的數值。在ADG 5412閉鎖保證家族中的元件可以承受具有1ms脈衝的±500mA應力,而不會發生故障的情況。在ADI中的閉鎖測試是依據EIA/JEDEC-78(IC 閉鎖測試)而進行的。

(作者為ADI愛爾蘭Limrick開關/多工器事業群應用工程師)