現今,許多主流處理器應用軟體對效能的需求越來越高,以處理更高的資料傳輸速率、更多的媒體服務,與利用使用者介面的新功能,如:加密與安全防護。在應用市場中,當消費者需求成為產品開發的主要動力,供應商將面臨降低終端產品價格的挑戰。這不只是為了在既有市場競爭,而是在可支配所得遠低於西方國家的開發中國家中,開創新的市場。

有許多例子指出,聯網行動電腦、其他可攜式裝置、手機、PDA、視訊轉換器、遊樂器,以及汽車資訊娛樂裝置等應用,都需要低成本且高效能的特性。

消費者不僅期盼他們的產品能執行更多功能,更希望可攜式產品能具備更長的電池續航力。為了達到可以連續使用一整天的最低要求,手機、智慧型手機以及PDA製造商必須提供比以往更高的效率及超高效能。以智慧型手機為例,其應用效能需求從待機時的「非運作」狀態,到執行遊戲時的高運作模式,其系統架構必須能夠因應兩種極端的效能需求,同時維持極高的效率。

其中一種方法是使用多重核心處理器架構,來滿足尖峰效能的需求,並讓設計方案能因應極低功耗的運作模式。多核心元件具備極高的擴充效能及低功耗的特性,故能提供相當優異的設計彈性。

Cortex-A9 MPCore多核心處理器

Cortex-A9 MPCore多核心處理器整合了成熟且極為成功的ARM MPCore技術與後續的改良,簡化並擴展多核心解決方案的應用。Cortex-A9 MPCore把尖峰效能提高到前所未有的層次,並在同時支援設計彈性與各種新功能,從處理器與系統層級著手,進一步降低與控制功耗。

Cortex-A9 MPCore針對的產品,也為行動裝置帶來超越現今解決方案的優異尖峰效能,利用ARM MPCore的設計彈性與先進電源管理技術,在緊縮的行動電力預算下維持運作。

利用可擴充的尖峰效能,這款處理器的效能能夠超越現今同級的高效能嵌入型元件,並為更廣泛的市場帶來持續的軟體投資。

| 《圖一 Cortex-A9 處理核心的設計空間區隔》 |

|

滿足多重市場的需求

Cortex-A9處理器為各種市場應用提供可擴充的解決方案,從手機市場到高效能的消費性與企業級產品,Cortex-A9處理器都能滿足以下共同需求:

- ●達到更高的效能,並提高能源效率,藉以降低功耗

- ●替要求最嚴苛的應用提高尖峰效能

- ●讓多種元件能共用軟體與工具投資

Cortex-A9處理器不僅維持完全的應用相容性,也運用了Cortex-A9 NEON媒體處理引擎(MPE),或浮點運算單元(FPU)來提昇特定應用的效能,進一步擴展這些處理器的市場應用範疇。每種建置的設計組態,都能夠提供充裕的彈性,以適應不同的應用與市場特性。

(表一) Cortex-A9 處理器應用範例

新一代裝置 |

Cortex-A9解決方案 |

手機、聯網行動電腦 |

新一代高階裝置(1500-3000DMIPS)

- 2至3個內建IEM技術與可調適關機功能的處理器

- 32K指令與資料快取,256至512K共用L2快取,運用PL310、可分區AXI

- NEON技術的媒體處理引擎,搭配GPU

|

中階、降低成本(900-1500 DMIPS)

- 單核心處理器搭配NEON或浮點運算單元

- 16K或32K指令與資料快取

- 128-256K L2快取,使用PL310、單AMBA AXI匯流排

|

多功能的量產市場(600-900 DMIPS)

- 內建浮點運算單元的單核處理器

- 16K指令與資料快取、單AXI

|

消費性與汽車資訊娛樂裝置 |

消費性產品:使用者互動功能(800-3000 DMIPS)

- 1至4個核心處理器,支援系列裝置的設計擴充性

- 32K指令與資料快取,搭配0至512K L2快取

- 支援先進媒體與DSP處理作業的NEON技術

- 先進匯流排介面單元,能在晶片內部的3D引擎與網路介面MAC之間進行高速的記憶體傳輸作業

- AMP組態,讓即時RTOS使用不同的CPU

|

網路/家用閘道器 |

企業市場(4000-8000 DMIPS)

- 3至4個核心的效能優化方案

- 32K+64K指令與資料快取

- 512K-2MB L2快取,兩個64位元AMBA AXI介面

|

消費性裝置(800至1500 DMIPS)

- 運用附屬加速器的1x或2x多核心元件

- 32K+32K指令與資料快取,搭配256-512K共用L2快取

- NEON或VFP,協助提供媒體閘道器或服務

|

嵌入型產品 |

嵌入型媒體與影像處理(800至2000 DMIPS)

- 2x多重核心元件,運用附屬加速器

- 32K+32K指令與資料快取,搭配256K共用L2快取

- 浮點運算單元支援postscript檔案以及影像處理與強化功能

- 透過特定的AMP/SMP建置方案移植程式碼

|

特殊應用最佳化

Cortex-A9 與Cortex-A9 MPCore 應用等級處理器,皆具備ARMv7架構功能以及其他豐富特色,能針對特殊應用與一般用途的設計,帶來高效能與低功耗的解決方案。

(表二) Cortex-A9 處理器特色

功能特色 |

優勢 |

高效率超純量管線 |

超過2.0 DMIPS/MHz的業界領先效能,不僅帶來前所未有的尖峰效能,還維持低功耗的效益,藉以延長電池續航力、低成本的封裝與運作模式。 |

NEON 媒體處理引擎 |

加快媒體與訊號處理功能,以增進特殊應用效能,帶來匯整應用軟體研發與支援的便利。 |

浮點運算單元(FPU) |

大幅加快單倍與雙倍精準度純量運算作業速度。效能比前一代的ARM 浮點運算單元高出一倍,此單元提供領先業界的影像處理、繪圖,以及科學運算能力 |

最佳化的Level 1 快取 |

具備最佳化效能與功耗的L1快取,結合最低存取延遲技術,提高效能並降低耗電量。同時提供快取連貫性的選項,以改進處理器間的通訊,或支援豐富的SMP作業系統,達到簡化多重核心的軟體開發作業的目標。 |

Thumb-2 技術 |

減少30%儲存指令時所使用的記憶體,並提供傳統ARM程式碼的尖峰效能。 |

TrustZone 技術 |

確保可靠地建置各種從數位版權到電子付費的安全應用,並提供技術與產業夥伴的廣泛支援。 |

Jazelle RCT 與DBX 技術 |

在及時與提前編譯位元組碼語言程式碼時,讓程式碼長度減少3倍,並支援直接執行Java指令程式碼,藉以加快傳統虛擬機器的速度。 |

L2 快取控制器 |

支援各種高頻率,或需要降低功耗以存取晶片外部記憶體的設計,提供低延遲、高頻寬模式存取高達2 MB的快取記憶體。 |

程式追蹤巨集與CoreSight 開發套件 |

結合這些元件,讓軟體研發業者能以不干擾的方式追蹤多個處理器的執行歷史,並同時與時戳修正資料,一起儲存到晶片內緩衝區,或透過標準追蹤介面儲存到晶片外部元件,藉此改進開發與除錯階段的可視性。 |

先進的微架構

精心設計的Cortex-A9微架構,針對追求低矽元件成本的嵌入型元件,提供最大化的處理效率,並排除超高效頻設計缺少效率的缺點。透過各種合成技術,該處理器能讓元件能達到超過1 GHz的時脈頻率,並提供超高的省電效率,進而帶來更長的電池續航力。

| 《圖二 Cortex-A9 微架構的結構以及單核介面》 - BigPic:914x563 |

|

Cortex-A9 MPCore技術

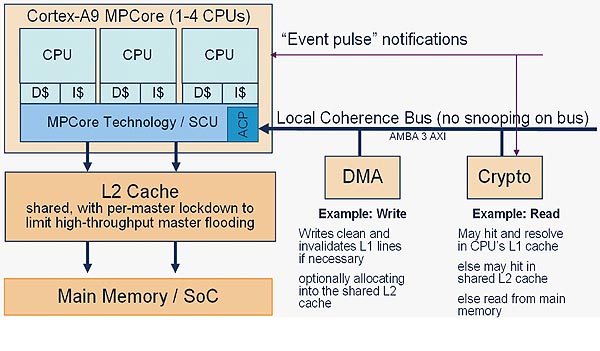

Cortex-A9 MPCore多核心處理器提供一個設計組態的處理器,利用整合快取的協調方式支援1至4個CPU。每個處理器能獨立設定自己的快取容量,並決定是否支援浮點運算單元、MPE、或PTM介面。此外,任何組態的處理器都可連結加速器連結埠( Accelerator Coherence Port),允許其他無快取的系統主控端週邊元件與加速器,如:DMA引擎或加密加速器核心,連結至處理器的L1快取。Cortex-A9 MPCore還整合一個相容整合中斷的中斷控制器架構與通訊系統,搭配專屬週邊元件,用來提高效能與軟體可移植性,並可被組態以支援0(舊型旁通模式)或224個獨立中斷來源。這個處理器也能支援單一或兩個64位元AMBA 3 AXI互連介面。

| 《圖三 Cortex-A9 多核心處理器》 - BigPic:599x352 |

|

Cortex-A9 MPCore多核心處理器包含一個以通過矽實體驗證的ARM MPCore技術增強版,能夠支援可擴充的多核心處理功能:

偵測控制單元(Snoop Control Unit, SCU)

偵測控制單元是ARM多核心技術的中央控制核心,在所有搭載MPCore技術的處理器中,負責管理互連、仲裁、通訊、快取之間與系統記憶體的資料傳輸、快取連結、以及其他多核心功能。

Cortex-A9 MPCore處理器首度將這些功能擴展至其他系統加速器及非快取的DMA週邊元件上,讓各元件共享處理器的快取架構,以增進效能並降低整個系統的耗電量。這項系統不但連結設計,亦因不必維護每個作業系統之間的軟體關聯性,而降低軟體的複雜度。

加速器連結埠(Accelerator Coherence Port)

在SCU上的AMBA 3 AXI相容從屬端介面,為各系統的主控端提供一個互連點,使整體系統效能、功耗,或是其他軟體簡化因素,能夠更直接地與Cortex-A9 MPCore處理器介面連結。此介面扮演標準的AMBA 3 AXI從屬端,並在對連結元件無額外相關要求的條件下,支援所有標準的讀取與寫入交易。

然而,任何接觸到記憶體中關聯區域的讀取交易,都會和SCU進行互動,以測試要求的資訊是否已儲存在處理器的L1快取。若資訊已存在快取內,就會直接傳回到發出要求的元件。若資料沒有儲存在L1快取,在轉到主記憶體前,仍有機會搜尋L2快取。接觸到任何關聯記憶體區域的寫入交易,SCU會在動作被轉至記憶體系統前,執行連結。寫入交易也可轉至L2快取,藉以排除因直接寫入晶片外部記憶體而衍生的功耗與效能影響。

| 《圖四 加速器的連結埠》 - BigPic:599x350 |

|

中斷控制器(Generic Interrupt Controller)

運用最近完成標準化與架構化的中斷控制器,GIC提供豐富且彈性的方法建構處理器之間的通訊,以及系統中斷的傳遞與優先排序機制。在軟體控制下最多可支援224個獨立中斷,每個中斷能在CPU,硬體優先排序,以及作業系統與TrustZone軟體管理層之間傳遞。這樣的傳遞路徑彈性,加上支援作業系統的中斷虛擬化機制,創造了一個關鍵功能,讓使用半虛擬化管理器的解決方案能夠強化其功能。

先進的匯流排介面單元

Cortex-A9 MPCore處理器強化了處理器與系統之間的介面互連,提供許多先進功能,達到系統效能最大值,並針對各種系統單晶片設計方法帶來額外的彈性。

透過支援單倍或雙倍64位元AMBA 3 AXI主介面的設計組態,處理器能在CPU速度下提供全負載的交易平衡機制,支援速度超過12 GB/s的系統互連介面。第二個介面亦可定義成處理全域定址空間的交易過濾器,為系統設計增加彈性,在處理器架構中立即分割定址空間。

每個介面亦提供不同的CPU與匯流排頻率比,包括同步半時脈比,藉以替支援採用DVFS或高速晶片內記憶體的設計增加設計彈性,並改進系統頻寬。此外,產品還可完全支援ARM智慧型電源管理(IEM)功能。

運算引擎加速功能的特定應用

除了各項最佳化的標準架構功能外,Cortex-A9與Cortex-A9 MPCore處理器皆能支援以下功能:

先進的L2 快取控制器

ARM L2快取控制器 (PrimeCell PL310)與Cortex-A9處理器一起研發,提供一個最佳化的L2快取控制器,能配合Cortex-A9處理器的效能與總處理能力。

PL310的每個介面能支援高達8個未完成的AXI交易,加上每個主控端與方向的鎖定機制,能透過加速連結埠在多個CPU或元件之間進行管理分享,有效運用PL310作為加速器與處理器之間的緩衝區,增進系統效能並降低相關功耗。

PL310亦含有Cortex-A9先進匯流排介面單元的各項功能,故能支援同步式1/2時脈週期比,以降低高速處理器設計的延遲,且能對第二個主控端AXI介面進行位址過濾,以支援分割區域、分割頻率的設計,並快速存取晶片內的暫存記憶體。

PL310最高可支援2MB的4至6路關連式L2快取記憶體,支援與同位元與ECC支援RAM的選項性整合,並在處理器的時脈頻率下運作。先進的鎖定技術亦提供許多運用快取記憶體以作為連結加速器與處理器之間的傳輸RAM的機制。

Cortex-A9程式追蹤巨集 (PTM)

Cortex-A9 PTM為Cortex-A9處理器提供與ARM CoreSight技術相容的程式流程追蹤功能,能監看處理器實際的指令執行流程。Cortex-A9 PTM能搭配週期計數功能,監看所有程式碼的分支和程式流程的變動,以便進行設定分析。

此外,Cortex-A9 CoreSight開發套件能連結多個處理器的追蹤流程,且含有CoreSight元件,以對Cortex-A9 MPCore多核心處理器設計進行追蹤與除錯。

合成彈性與參考設計方法

Cortex-A9處理器充分利用合成設計流程的彈性,能針對任何晶圓製程與尺吋。透過持續與各大EDA廠商合作,以及各種實作參考設計方法(iRMs),Cortex-A9處理器的授權客戶能針對自己選擇的製程技術,對處理器進行客制化、建置、檢驗,及特性規劃。這些參考方法提供可預測的矽元件開發路徑,作為發展客制化設計方法的基礎,利用各種邏輯與實體合成技術。

除了iRM外,還可加入ARM Artisan前端元件庫檢視功能,以及預先編譯的RAM,來強化iRM提供處理器建置流程的功能,並提供遠比先前更完整的參考解決方案。

(表三) Cortex-A9的FPU與MPE功能說明

Cortex-A9 浮點運算單元 (FPU):

|

Cortex-A9 NEON 媒體處理引擎(MPE):

|

在搭配Cortex-A9處理器時,FPU提供高效能的單倍及雙倍精準度的浮點運算指令,相容於ARM VPFv3架構,並與前一代的ARM浮點運算協同處理器之間維持軟體相容。完全支援IEEE-754的浮點運算,其執行速度媲美先前的“run-fast” 高速模式,不會出現簡化軟體的受限例外,並進一步提高 浮點運算程式碼的速度。

此外,系統還加入額外的16位元浮點運算資料類型轉換指令,增進與嵌入型3D處理器之間的互動,如:ARM Mali 繪圖處理器。

Cortex-A9浮點運算平均效能比前一代的ARM浮點運算協同處理器多出一倍以上。一個Cortex-A9 FPU能大幅改善精密繪圖、3D、影像處理、以及科學運算解決方案的性能。 |

Cortex-A9 MPE 能搭配Cortex-A9處理器,並提供一個具備Cortex-A9 浮點運算單元的效能與功能的處理引擎,加上由ARM Cortex-A8處理器首次推出的ARM NEON Advanced SIMD 指令集,進一步加快各種媒體與訊號的處理功能。

MPE延伸了Cortex-A9處理器的FPU,提供一個quad-MAC以及額外的64位元與128位元暫存器,支援為數眾多的SIMD運作模式,每個週期能處理8、16、32位元整數與32位元浮點運算資料。

為進一步強化SIMD功能,MPE亦支援混合資料類型,排除封裝/解封裝所耗費的資源,以及結構化的載入/儲存功能,讓資料不必在演算格式與機械格式之間來回轉換。

運用MPE亦能增加FPU可使用的暫存器檔案容量,並支援32個雙倍精準度暫存器,同時保有Cortex-A9處理器的32/64位元純量浮點運算與核心整數運算效能。 |

結論

Corte-A9與Cortex-A9 MPCore專門滿足單核心與多核心處理器的設計需求。通用的微架構結合各項功能,為處理器核心與SoC提供增強的架構功能、效能、以及省電效率。

單核心處理器為現有的ARM11等級元件提供更高的效能與省電效率,帶來強化的功能與更低的功耗,讓行動設計能延長電池續航力。各種實作特性亦帶來完全的架構軟體相容性,讓業者能以更低的成本達到Cortex-A8等級的效能,使相關軟體投資能拓展至市場。

MPCore處理器提供先進的電源管理功能,進一步降低耗電量,並在越來越多的市場與應用中,超越產品對功耗的需求。Cortex-A9 MPCore亦提供前所未有的擴充效能,發展許多以往無法享受ARM處理器省電設計的市場。

經過特別設計的完整支援技術,能整合至Cortex-A9處理器,進一步提昇效能,滿足各種特殊應用與市場的需求,特別是無線、娛樂、影像、以及其他高階多媒體應用。