以往的類比電路設計師都採用提升電源電壓和操作電流來提高裝置的運行速度和動態範圍,但隨著日漸重視的能源效益,這方法已不再適用。現今,除了要追求更高的操作頻率、可用頻寬、雜訊性能和動態範圍之外,還必須維持功耗不變或甚至把它降低。也就是說,業界追求的是性能/功率比更佳的元件。

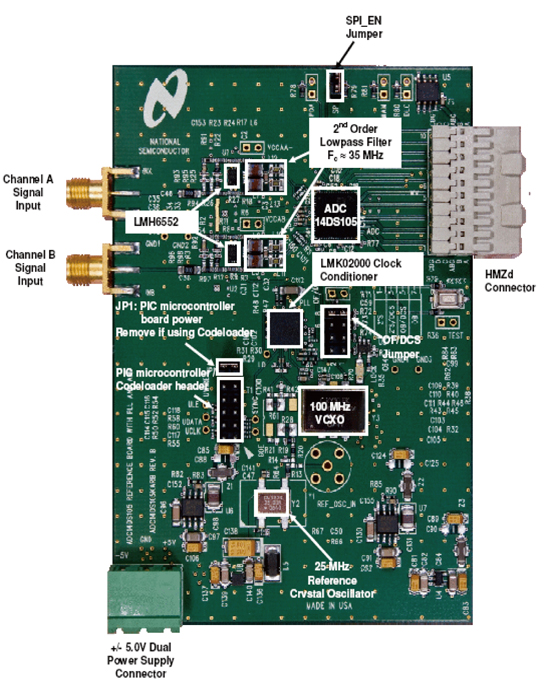

美國國家半導體的PowerWise產品採用了創新的架構和先進的製作製程來開發,不僅高性能而且功耗相當低。本文將採用圖一中的參考設計平台來展示如何利用高能源效益的類比到數位轉換器(ADC)、全差動放大器和時鐘調節電路來開發出一個完整的類比系統。接下來先介紹PowerWise技術。

| 《圖一 完整的參考設計電路板,當中包含有ADC、全差動放大器和時鐘調節器電路》 |

|

電路設計師的工具選擇

開發出色的電路需要優秀的電路設計和採用合適的製程技術。然而,電路等級的設計屬於公司的專利權資訊,很難去評估有關設計的專業知識或能力。不過這裡有其他比較容易的方法可獲取技術上的專業知識。無疑的是,「創新」是任何技術公司的活力泉源,而「專利」則是評量創新能力的最有效工具。美國國家半導體每年獲得超過200項專利,當中大多數與製程和類比技術有關,直至現在美國國家半導體已擁有超過2900項專利。

為特定元件量身訂造的製程技術

用來開發類比/數位轉換器(ADC)的製程技術並不一定適合用來開發高頻的低雜訊放大器。事實上,公司一般都會使用幾種不同的製程技術,例如是CMOS、BiCMOS和SiGe等,而使用那一種則取決要求的元件參數而定。就算是電路的設計如何完美,假使沒有優秀的製程技術配合也是枉然。

美國國家半導體的先進製程技術開發小組長久以來專注於開發高度特徵化和模型化、可製造和可靠,以及創新和獨特的製程技術。特別的電晶體是由公司內部的工程部通過不同的製程技術來開發,使產品可在最低的功耗下發揮出最佳的類比性能。不同於其他大多數的半導體供應商,美國國家半導體採用純CMOS技術去設計大部份最新的ADC。

今天,CMOS技術無處不在,原因是CMOS的邏輯閘仍沒有任何的靜態功耗,而且擁有較高的驅動電流和速度。考慮到ADC內包含有大量的數位電路,因此用純CMOS技術去實現電路設計便可比用BiCMOS時更低的功耗。數位CMOS閘電路在直流模式下不會消耗電流,但雙極的閘電路即使在直流模式下都需消耗電流,因為電路需要偏置電流來維持性能參數。結果,晶片中的數位部份會消耗較多的電流,使得整體的功耗較大。

此外,美國國家半導體亦特別開發出像是VIP10製程來配合放大器電路的設計。VIP10是一種高速、介質隔離的互補雙極(complementary bipolar)電路製程,它在一片鍵合晶圓(bonded wafer)上採用深槽(deep trench)技術來作出完全的介質隔離,以及達到最佳的高速放大器性能。用在鍵接晶圓上的深槽技術可將寄生電量儘量降低以獲得更優的功率/頻寬性能、較低的失真和更細小的晶片尺寸。採用高性能NPN和PNP電晶體的互補雙極電晶體設計可以為現今的高速放大器帶來最佳的性能組合,包括高頻寬、低功耗、低電源電壓、大輸出擺幅、高輸出電流和低失真。對於雙極電晶體來說,最常用的AC品質因素是過度頻率(FT),在這頻率下共發射極電流增益下降到單位級。

在VCE=5V下,VIP10 NPN和PNP的FT分別為9GHz和8GHz,大約比同類競爭產品的製程高出50%。電晶體的高FT意味著在某給定操作點下其發射極-基極擴散電容將會處於低數值。配合VIP10電晶體,美國國家半導體可以設計出頻寬超過1GHz或頻寬在100MHz範圍以內的放大器,而其功耗可以非常低。

這是由於內部階段(internal stage)即使在很低的操作電流下都會出現低的相位位移,原因是擴散和寄生電容同時都被大幅削減。對於某些雙極製程來說,FT可以在較低電壓下大幅地下降,但若採用VIP10製程,那即使Vce=1V,FT都可維持在高水平:NPN可達7GHz而PNP可達5GHz。公式一表示出一個雙極電晶體的過度頻率是如何計算出來。

- (公式一)

- 其中:

- , , ,

- 公式中:

- k是玻滋曼常數(Boltzmann’s constant);

- T是絕對溫度;

- Cte是發射極電容;

- q是電子的單位電荷;

- IC是集電極電流;

- WB是基帶頻寬;

- μB是電子移動性;

- rcs是集電極電阻;

- Ccb是集電極電容;

- Xs是集電極空間電荷區的寬度;

- 而vx則是集極空間電荷區的飽和速度。

創新技術

上述已探討過最佳的電路設計方法、專利架構和先進的製程技術,讓電路設計師可以運用業內最出色的技術。這些強化系統能夠使設計人員在競爭激烈的市場中開發出與眾不同的產品。為了進一步超越競爭對手,系統架構工程師必須追緊未來的工業發展。創新的技術例如PowerWise可以使數位處理器(例如是DSP或FPGA等)中的DSP或FPGA功耗降低達70%。

PowerWise採用自適應電壓調節(Adaptive Voltage Scaling;AVS)和臨界值調節技術,自動將數位邏輯電路中的活躍和漏電功耗減到最低,而且期間所牽涉的系統開銷亦非常少。PowerWise技術是一種可供所有電路開發商使用的先進系統能源管理方案,其內容不單完備而且還可提供詳細的智慧財產資訊。透過使用簡單的標準硬體介面,加上美國國家半導體與其他業內知名廠商如ARM、TSMC、UMC和Synopsys的合作,確保了這項技術可應用到任何的CMOS製程上,而且設計工具和流程都已標準化。

建立完整的類比系統

參考設計(reference design)對於工程人員來說相當重要,它提供一個良好設計作業的樣板,尤其是如何在不增加功耗的前提下提升性能。大多數困難的設計問題,例如是正確的元件選擇和放置,以及佈局和佈線等,都可在這些設計參考中找到答案。美國國家半導體多年來一直幫助客戶創建高性能類比系統,現在已成功建立了一個設計參考庫,能夠說明如何設計最佳的系統性能。以最新加入參考庫的ADC14DS105KARB參考設計為例,它採用了最新的PowerWise 家族LMH6552 1.5GHz差動驅動器來作為訊號路徑的一部份。這元件與高速的ADC14DS105資料轉換器和定時方案結合在一起後,便可為工程人員提供一個設計測量儀表的最佳起點。

ADC14DS105KARB接收器參考設計板

ADC14DS105KARB是一個近零中頻接收器(near-zero IF receiver)參考設計板,它所使用的元件如下:

- 兩個LMH6552 1.5GHz 頻寬差動電流回饋放大器;

- ADC14DS105 帶有LVDS輸出的14位、1GHz、雙路、105MSPS類比/數位轉換器;

- LMK02000低抖動精密時鐘調節器,它帶有一個可在100Hz到20MHz頻寬範圍內提供128fs抖動的整合鎖相迴路(PLL);

- 數個高能源效益的電源管理電路。

ADC14DS105KARB(圖二所示為其方塊圖)是一塊中頻接收器子系統參考設計板,它採用一對LMH6552差動驅動器和一個雙路ADC,可以立即測試適用於直流電至40MHz訊號頻率的正交直接轉換或近零中頻接收器。這接收器架構現已被廣泛應用到WiMAX和WCDMA接收器系統。

由於ADC的輸入頻寬高達1GHz,而差動放大器增益級的頻寬則高達1.5GHz,因此若輸入訊號不超過40MHz,大訊號的訊號/離訊比可達73.3滿刻度分貝值(dBFS),而無雜散訊號動態範圍(SFDR)則超過85dBFS。這款電路板除了採用LMH6552之外,還安裝了美國國家半導體的14位、105MSPS、低失真、低雜訊、並可輸出串列LVDS資料的雙通道類比/數位轉換器ADC14DS105、低抖動時鐘調節器LMK02000以及多個具能源效益的電源管理電路。

LMH6552是一個高性能全差動放大器,它能提供驅動14位元高速資料獲取系統所需的超強訊號保真度和寬闊的大訊號頻寬。通過採用專利的差動電流模式輸入級架構,使LMH6552能夠在不犧牲響應平坦度、頻寬、諧波失真或輸出雜訊性能下在增益大於一個單位級下操作。

配合外建的增益集電阻器和整合式的共模回饋,使得LMH6552可被配置成一個差動輸入到差動輸出或訊號單端輸入到差動輸出的增益級。LMH6552的輸入端可作交流耦合或直流耦合,因此其應用範圍非常廣泛,包括通訊系統及高速數示波器的前端電路。

LMH6552的電流回饋拓墣使裝置即使在高增益值下,只需選擇合適的回饋電阻(RF1、RF2),便可提供有超強增益平坦度和雜訊性能的增益和頻寬獨立性。在大多數的應用中,RF1都被設定成等於RF2,因此增益是由RF/RG的比例所決定。

LMH6512的資料表針對各種各樣的增益建議出最佳的回饋電阻器數值。無論是過大或過小的RF都會對穩定性構成影響。在許可的情況下,回饋電阻器亦可以用來調節頻率響應。

電流回饋放大器的的優點是相對於其對手電壓回饋需要較少的內部增益級。通常一個電流回饋放大器主要包含有一個輸入緩衝器、一個增益級和一個輸出緩衝器。擁有較少的增益級意味著經過開放迴路電路的延遲會較少,從而在相同的功耗下能獲得較大的頻寬。

圖三中的基本電流回饋(CFB)拓樸是一個單級放大器。電路中的唯一高阻抗節點是在輸出緩衝器的輸入。VFB放大器通常需要兩個或以上的增益級才能獲得足夠的開放迴路增益,這些附加的增益級不單會增加延遲,而且還會降低頻寬的穩定性。

圖四說明了放大器的參考電路板配置。當中的輸入是50和直流耦合。LMH6552被配置成單端到差動模式轉換,而ADC14DS105的VCOM輸出會用作放大器的共模輸入。每一個放大器都被配置成有6分貝的增益,因此最大的輸入訊號電平為1Vp-p,並在放大器的輸出處產生出2Vp-p。這裡建議放大器最好由一個雙電源軌來供電(±5VDC),但電路板亦可被配置成在單電源模式下操作,只需在VCCAA-和VCCAB-處安裝跳線便可,而詳細資訊可參考LMH6552資料表中有關LMH6552單電源操作的部份。為了獲得最佳的失真性能(最佳SFDR),建議採用一個低雜訊訊號產生器來驅動評估板的訊號輸入,而訊號產生器的輸出應該經過帶通濾波以抑制由訊號產生器所引致的諧波失真,以及容許進行精確的雜訊和失真性能測量。然而,跟隨在LMH6552之後的43MHz的5階低通濾波器可過濾訊號產生器的寬帶雜訊,進一步改善ADC的雜訊性能。濾波器輸出會被類比/數位轉換器取樣。

ADC14DS105是業界第一款帶有串列化LVDS輸出的14位高速、1GHz FPBW的雙路類比/數位轉換器。裝置的串列化LVDS輸出可大大地簡化電路板的佈局,原因是它大幅地減少了需要跨過電路板或在電路板之間的導線數量。

| 《圖四 LMH6552電路和5階低通濾波器》 - BigPic:566x311 |

|

用來替類比輸入取樣的ADC時鐘訊號是由一個經LMK02000精密時鐘調節器控制的VCOX所產生。該LMK02000為用戶提供一個設有時鐘分配區的超低雜訊鎖相迴路(PLL),其可提供5個LVPECL輸出和3個LVDS輸出(全為差動)。

每一條在LMK02000上的時鐘輸出通道均包含有一個除法器區塊和延遲調節時鐘。LMK02000一般都會跟一個低抖動的VCOX連接在一起。在這情況下,一個Crystek型號的CVHD-950X-100.0可提供一個單端CMOS時鐘訊號來驅動ADC的時鐘輸入。LMK02000的鎖相迴路可把這個VCOX鎖定到一個25MHz的參考振盪器(Connor-Winfield型號CWX823),而LMK02000的鎖相迴路計數器、相位檢測器和電荷泵是用PIC微控制器電路板來編程,詳情請參考用戶指南。

LMK02000的訊號抖動僅為128fs均方根(輸入的時鐘範圍由100Hz到20MHz)。圖五表示出時鐘的相位雜訊性能,當中的資料是在LMK02000的CLKout4測量出來。從VCOX產生出來的單端時鐘訊號會供給ADC14DS105的CLK輸入。

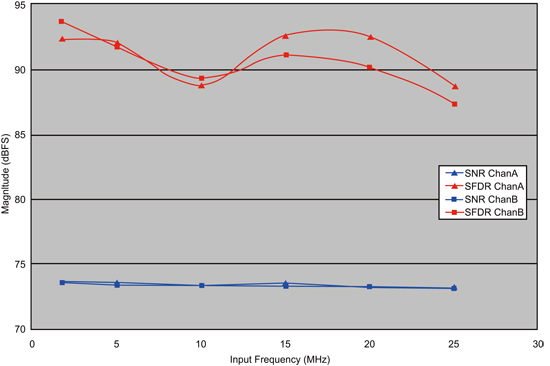

| 《圖六 典型SFDR和SNR性能與輸入頻率的關係》 |

|

LMK02000精密時鐘調節器將多種功能結合在一起,包括抖動清除/重新調節、倍頻和參考時鐘分配。裝置整合了一個高性能的整數-N鎖相迴路(PLL)、一個局部整合環路濾波器、三個LVDS輸出和5個LVPECL時鐘輸出分配區塊。

圖六所示為差動放大器、帶通濾波器和ADC的結合通道響應,注意圖中最佳的動態性能和通道間的匹配性。

---作者為NS美國國家半導體資深應用工程師---