年度全球网际网路流量预计在未来五年内会出现爆炸性的成长(思科视觉网路指标)。这种成长是由越来越多的装置连线及在内容消费的上升所导致。

为了支持此预测的成长,必须相对地提升资料由网路基础设施交付的速度。目前业界正努力让输送量提升两倍甚至四倍,且每通道可提供 56Gbps 或 122Gbps I/O。

不归零(NRZ)发讯方案已不再能在较低频宽的通道上支援可靠的56Gbps输送量,由于NRZ的频率讯号内容会随着位元速率线性增加。针对相同的资料速率,仅需一半频宽(如 NRZ)的备用调变方案(例如PAM-4)将可提供所需的效能。

比较 PAM4 语 NRZ

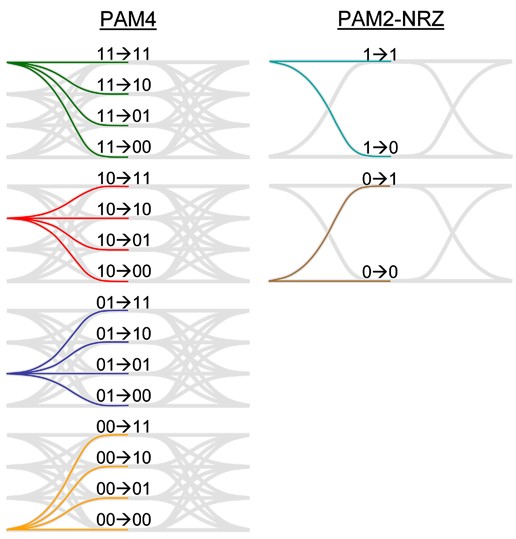

| 图1 : PAM4语NRZ利用不同的讯号位准和过渡码型。 |

|

图1为PAM-4与NRZ的快速浏览,显示PAM-4可支援4种位准(标记为位准0、位准1、位准2、和位准3),每单位间隔可传输两位元的资料,相较而言,NRZ 的每单位间隔仅可传输1位元的资料。

PAM-4发讯中的4种位准会产生三个相互依存的眼图,从其中一个位准转换到另一个时将会影响其他眼图。 PAM-4 讯号的三个眼上皆可执行眼图量测(类似于在NRZ眼上执行的量测),同时亦可在整体封包上执行另外一个整体外眼量测。

表1 PAM4 和 NRZ 发讯比较

? |

PAM-4 |

NRZ |

每 UI 位元数 |

2 |

1 |

位准 |

4 |

2 |

上升/下降边缘 |

6 |

2 |

转换 |

12 |

2 |

每 UI眼数 |

3 |

1 |

范例:PAM4 语 NRZ 眼图

‧垂直眼开口(眼高度) @ BER

-在相同的电源电压下,PAM4个别眼高度为NRZ的33%

-由于鲍率仅有一半,PAM4 可忍受更低的损耗

‧水平眼张口(眼宽度) @ BER

-由于鲍率仅有一半,PAM4个别眼宽度为NRZ的200%

-PAM-4眼宽度是由非相邻位准之间的转换减少

成功的 PAM4 设计

与NRZ不同,设计中包含了多年来所建立的大量知识,这可让设计和验证团队提升现有设计的发展,达到更高的效能。但是,由于PAM-4需要处理多位准发讯,这引入了复杂的发射器和接收器,且改变了在装置和系统位准上执行的设计、模拟、特性分析和验证活动。

传统上,模拟(设计)与量测(验证)在不同的开发阶段和不同的职能团队中进行,并依赖不同的方法和工具来达成其目标,即使是针对同一个产品。

在透过通道传输时,由于讯号失真,PAM-4讯号几乎总是有一个闭合的眼。在模拟与量测环境中,等化器可用于扭转失真、还原讯号和开放讯号眼。传统上,设计环境使用与各种EDA工具相容的IBIS AMI模型,而与此相反,参考等化器可用于进行量测系统中的量测。

此外,实验室量测经常出现电脑模拟中不存在的设备:测试夹具、电缆、接投、射频切换器、测试设备等。

其结果是,如果不考虑这两个方法之间的差异和现实世界的限制,模拟结果便可能与量测结果不一致。仅根据模拟或量测结果,而不包含来自设计和验证阶段且彼此不同意的资料,这样所做出的结论可能毫无意义。

为引导和实现满足现实要求和余裕的产品设计,至关重要的是纳入这些真实世界的设备,并使用相同的分析方法,打造出高效和准确的模拟和量测工作流程。缩减设计和验证阶段之间的差距,并让团队使用相同的参考资料和分析方法,谈论同样的主题,进而推动在市场中进行更快速的产品部署行动。

缩小模拟和量测差距

挑战

在验证过程中,最新的PAM-4 发射器(TX) 未通过矽后(post-silicon)测试,不符合产品规格;其设计是以矽前(pre-silicon)模拟为基础,确实显示符合产品规格,而经过签署同意。在仔细分析发现:

1.在模拟期间会计算发射器的输出,但会忽略在实验室验证量测(包括测试夹具、接头和电缆)期间的实际测试条件,而直接的结果即是模拟结果过于乐观;

2.在进行量测前,讯号已使用参考接收器(RX)等化器进行等化处理(大多数的测试要求常用)。与此相反,设计团队则使用IBIS AMI接收等化器模型来模拟和评估讯号(EDA 使用者常用)。

模拟/量测关联要求发射器(TX)、接收器(RX)和通道需精确建模,并考虑在实验室中的真实场景,如参考通道、电缆、夹具、射频切换器,这些装置均会对讯号产生影响。

实验室设定包括测试夹具,可从装置下方击穿讯号,并将其路由至接头。电缆之后可用于将测试夹具连接至示波器以进行量测。将待测装置(DUT)连接至示波器的半公尺长SMA电缆会在第一个谐波上引入额外约5dB 的插入损耗,同时由于使用测试夹具和可能使用的射频切换器,也会产生更多的损耗,如果有更多讯号需要进行特性分析,则会导致余裕减少。

另外,参考等化器处理与设计的IBIS AMI机型不同的讯号。从(1)和(2)的结果看来,在测试期间,DUT未能满足眼高度和眼宽度规格。

图2设计人员在DUT测试点(蓝色)模拟讯号的完整性,而测试人员则使用额外的夹具和设备(红色)量测讯号。

由于存在测试夹具、设备和使用不同的Rx方法,量测结果会与设计模拟不一致。

解决方案

若量化连结中各元素的影响程度,并使用模型将其纳入模拟和量测工作串流,将会降低设计阶段和验证阶段之间的差距,以早期发现并解决缺陷。

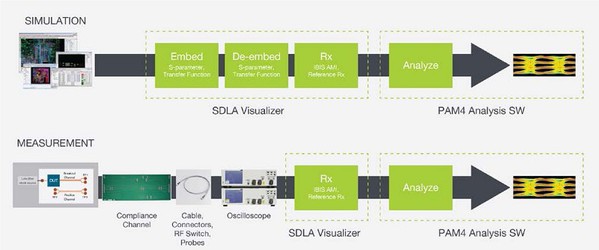

在矽前设计和分析阶段,Tektronix的最新分析和量测解决方案可让客户能执行之后在实验室用于签署同意的相同测试。

‧序列资料链结分析(SDLA)显影仪是适用于即时示波器上高速通讯协定的连结分析解决方案;可在量测和模拟资料上运作,其特点是:

-使用虚拟探测和DSP解嵌入/嵌入技术,进行各种可能的探测,并可视化所需的资料;

-移除/纳入测试设备(电缆、探棒、夹具等)的影响以达成准确的结果。此外,SDLA随附许多P76xx、P75xx和P73xx系列探棒机型及DPO/DSA/MSO70K系列示波器的输入阻抗机型,并可自动进型识别;

-模型参考接收行为,以及ISIS-AMI支援,与EDA设计输出相容。

‧DPOJET / PAM4分析功能会执行自动讯号量测及特性分析,为NRZ(DPOJET)和PAM-4(PAM4分析)发讯提供准确和全面的抖动和眼图分析,简化讯号完整性调查及高速序列、数位和通讯系统设计的最佳化程序;透过预设组态,支援各种已建立和新兴的标准(电子和光学),同时还为进阶的使用者提供了完全可自订的选项。

| 图3 : Tektronix的量测相关解决方案,可让设计人员能执行之后在实验室用于签署同意的相同测试。 |

|

模拟/量测关联性

为了证明解决方案的模拟/量测关联性,我们与Cadence合作,并采用了其Sigrity SI / PI分析工具。如图5所示,Sigrity包含了嵌入和解嵌入的S参数,因此,SDLA显影仪会使用由Sigrity移植的IBIS-AMI模型,针对模拟和量测路径执行Rx等化处理。

发射器属性

‧资料速率:25.78125 GBps

‧发讯:PAM4

‧Tx等化:5-tap FIR(1个前驱,3个后驱)

‧资料码型:PRBS7

通道属性

‧IEEE 802.3bs 400 GB专案组库,中距离/晶片到晶片通道,具单一连接器

‧插入损耗:18.2 dB @基本

接收器属性

‧自动增益控制(AGC)

‧适应性2极连续时间线性等化器(CTLE)

‧15-tap决定回馈等化器(DFE)

以下图片显示了设计/模拟阶段之间的结果相关性和验证/特性分析。

(本文作者沉忠荣微太克科技技术经理)