Certus-NX 是萊迪思Nexus 技術平台上的第二款產品,它將為更廣泛的應用帶來FD-SOI 製程的優勢。這些通用 FPGA 提供低功耗、小尺寸和靈活的 I/O,PCIe Gen2 和千兆乙太網介面以及高級加密功能。它們適用於智慧家庭、IoT、消費電子網路、馬達控制等多個領域的應用。

Certus-NX 將萊迪思 Nexus FPGA 技術平台的優勢帶到了新市場,主要針對需要 PCI Express 和千兆乙太網互連的應用。新產品系列有兩種型號,分別擁有 17K 和 39K 邏輯單元。較大的 Certus-NX-40 還提供 PCIe Gen2 介面,可連接主機處理器、無線或有線通信晶片以及其他許多元件。兩種型號均通過硬核支援千兆乙太網,提高了性能和功效。新產品的封裝尺寸遠小於競品的同時,I/O 密度增加了一倍。

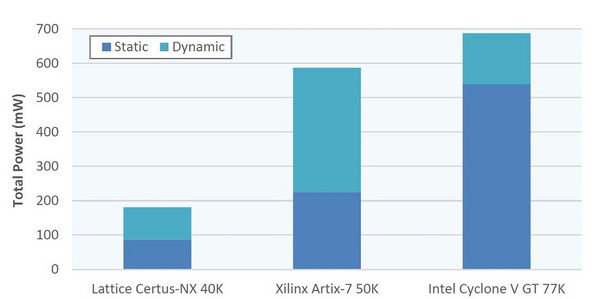

Nexus 平台的獨特之處在於採用了 FD-SOI 製程。這與之前的 CMOS 製程相比有很大區別,能夠極大降低功耗。如圖一所示,Certus-NX 比英特爾和賽靈思的同類產品功耗低3-4倍。Certus-NX的配置時間極短,能夠讓系統快速啟動。該元件還擁有驗證和加密硬體模組提升安全性。

| 圖一 : Lattice Certus-NX 器件。與英特爾和賽靈思的類似FPGA產品相比,Certus-NX的功耗降低了 70-75%。此功耗是針對 PCIe Gen2 介面,在嚴格測試環境下Tj =85oC,125MHz 測得的。(source:供應商功耗計算器) |

|

Certus-NX 主要面向網路中的各類控制和計算應用,包括在網路邊緣運行的自動化工業設備以及 5G 通信基礎設施和雲端資料中心。該 FPGA可以處理多種通信協議,其安全特性非常適合聯網設備。在許多情況下,該元件能在執行通信任務時分擔神經網路(AI)的負載。Certus-NX 還可以連接到模擬電機和感測器。

產品概述

Certus-NX FPGA提供了靈活的 I/O 和足夠的門電路來實現各種協議。該元件擁有多達39K 邏輯單元,為各類設計提供足夠的邏輯從而使用嵌入式 DSP 核實現神經網路或其他加速功能。其硬體加密模組可加速啟動代碼身份驗證的橢圓曲線(ECDSA)加密和 AES 批量加密演算法。該晶片還包括用於時鐘和資料恢復(CDR)的硬邏輯,支援高達1 Gbps 的乙太網資料傳輸速率,更好地支援了乙太網設計。通過結合該模組與足量的 LUT 實現乙太網協定,該晶片還可以實現與外部 PHY 晶片的SGMII 連接。

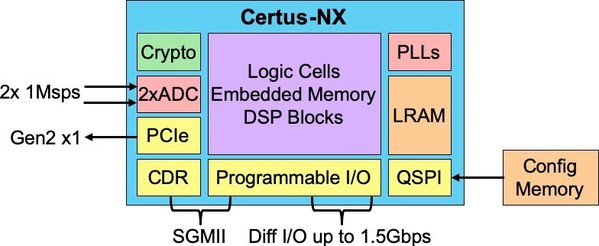

如圖二所示,Certus-NX-40 包括了PCIe Gen2 控制器的硬邏輯用於高速通信。該介面可連接單個速率高達 5 Gbps 的通道。兩種型號都有兩個 12 位逐次逼近(SAR)型模數轉換器(ADC),速率高達每秒一百萬個採樣(Msps)。對於其他協定,該晶片的可程式設計 I/O 可以實現高達 1.5Gbps 的單個介面和差分介面,包括 LVDS、subLVDS 和 DRAM (最高為 DDR3-1066)。對於這些介面,必須使用 LUT 資源實現控制器。晶片的邏輯結構包括LUT、嵌入式記憶體和用於 DSP 功能的 18x18 位乘法器。晶片邏輯機構外擁有一個大型RAM,可提供高達 2.5 Mbit 的額外存儲空間。

| 圖二 : Certus-NX 示意圖。全新 FPGA 擁有實現 AES 和橢圓曲線加密的硬核模組、用於十億位元乙太網(SGMII)的時鐘和資料恢復(CDR)、PCIe Gen2 控制器以及模數轉換器(ADC)。 |

|

FD-SOI製程可實現基體偏壓(back-bias),與 CMOS製程相比,漏電降低75%。在1.0V電壓下工作會降低有效功率。該製程還提高了晶片的可靠性。由於 FPGA 將其配置存儲在SRAM 中,因此隨機軟錯誤可能會導致元件故障(SEU)。相比於CMOS,FD-SOI製程能夠消除SRAM超過 99%的軟錯誤,從根本上避免了 SEU 的發生。

Certus-NX 產品提供各種封裝,其中最小尺寸僅為6x6 mm。該設計的低功耗特性減少了電源連接和接地的數量,從而為 I/O 留出更多空間。最小的封裝尺寸有 82 個 I/O,最大的封裝(14x14 mm)則擁有 192 個 I/O。萊迪思還縮短了將 FPGA 配置載入到 SRAM 所需的時間,從而縮短了啟動時間。若使用 Quad-SPI 連接外部快閃記憶體,Certus-NX-40 的啟動時間少於 14ms。而 I/O 在 3 毫秒內即可完成初始化。

產品比較

對於需要 PCIe 的應用,Certus-NX-40 與市場上的另兩款產品形成競爭關係,即英特爾的Cyclone V 和賽靈思 Artix-7 系列 FPGA。後兩者都是具有硬核 PCIe 介面、採用 28nm CMOS 製程的 FPGA。對於這款產品,選擇了有 50000 個邏輯單元的型號作為對比, 因為它們下一級較小的型號僅有 33000 個邏輯單元,遠低於 Certus-NX。如表一所示,這兩款競品的總存儲容量略大,對應的門數也較多,同時還提供更多的 DSP 模組。

?

|

Lattice

Certus-NX-40

|

Intel Cyclone V

5CGXC4

|

Xilinx Artix-7

XC7A50T

|

邏輯單元

|

39000 LC

|

50000 LE

|

52160 LC

|

總 RAM 大小

|

2.5 Mbit

|

2.8 Mbit

|

3.3 Mbit

|

DSP(18x18 乘法器)

|

56

|

140

|

120

|

硬體加密模組

|

AES, ECDSA

|

AES

|

AES

|

PCI Express

|

Gen2 x1

|

Gen1 x2

|

Gen2 x1

|

其他硬核 I/O

|

SGMII, ADC

|

DDR3

|

SGMII, ADC

|

最大 I/O 數量*

|

82–192

|

129–336

|

106–250

|

差分 I/O 速率

|

1500 Mbps

|

840 Mbps

|

1250 Mbps

|

IC 製程

|

28nm FD-SOI

|

28nm CMOS

|

28nm CMOS

|

最小封裝尺寸

|

6mm x 6mm

|

11mm x 11mm

|

10mm x 10mm

|

軟錯誤率(FIT)

|

19 次

|

Not reported

|

3102 次

|

配置時間

|

14 ms

|

139 ms

|

173 ms

|

估計功耗

|

181 mW

|

688 mW

|

539 mW

|

表一 用於 PCIe 設計的 FPGA。Certus-NX 提供更優的加密性能,支援乙太網和更快的 I/O 速度。該範圍對應不同封裝尺寸;*該資料是針對 PCIe Gen2 介面,在嚴格測試環境下 Tj =攝氏85度,125MHz 測得的。(source:除萊迪思外的供應商)

Certus-NX支援最優的加密,提供使用者模式AES 加速以及 FPGA 配置位元流的驗證(ECDSA)和加密。英特爾和賽靈思的兩款產品缺少驗證,僅支援AES配置。儘管Cyclone FPGA的兩個PCIe Gen1通道可以提供相同的總頻寬,但它不提供PCIe Gen2 支援,並且它不提供用於乙太網設計的硬核 CDR 模組。Certus-NX 的 I/O 速度最高,其封裝尺寸僅為其他產品的三分之一,可大大節省電路板面積。

對於不需要 PCIe 介面的應用,Certus FPGA 則與 Cyclone V E 系列和 Spartan-7 系列兩款產品競爭。

表二對比了 Certus-NX-17 與上述系列中邏輯單元數量相似型號。儘管 Certus- NX 的邏輯單元略少,但它的存儲空間更大,既有嵌入式記憶體又有外部的大型記憶體, 使其能夠緩衝更多資料或存儲更大的神經網路。與之前一樣,Certus-NX 在加密方面更為突出,I/O 速度更勝一籌。其 6x6 mm 的極小封裝尺寸所需的電路板面積不到兩款競品的四分之一,並且 I/O 密度約是它們的兩倍。Certus-NX 也是該組產品中唯一具有乙太網硬核的 FPGA。

?

|

Lattice

Certus-NX-17

|

Intel Cyclone V

5CEA2

|

Xilinx Spartan-7

XC7S25

|

邏輯單元

|

17000 LC

|

25000 LE

|

23360 LC

|

總 RAM 大小

|

3.0 Mbit

|

1. 9Mbit

|

1.9 Mbit

|

DSP(18x18 乘法器)

|

24

|

50

|

80

|

硬體加密模組

|

AES, ECDSA

|

AES

|

AES

|

其他硬核 I/O

|

SGMII, ADC

|

DDR3

|

ADC

|

最大 I/O 引腳數

|

78 I/O

|

223 GPIO

|

150 I/O

|

最大 I/O 密度

|

2.2/mm2

|

1.3/mm2

|

0.9/mm2

|

差分 I/O 速率

|

1500 Mbps

|

840 Mbps

|

1250 Mbps

|

IC 製程

|

28 nm FD-SOI

|

28 nm CMOS

|

28 nm CMOS

|

最小封裝尺寸

|

6 mm x 6 mm

|

13 mm x 13 mm

|

13 mm x 13 mm

|

表二 FPGA 用於網路邊緣設備。Certus-NX 擁有更小的封裝尺寸,抗軟錯誤性能比競品高 100 多倍,配置時間縮短 10 多倍。(source:除萊迪思外的供應商)

Certus-NX 系列產品利用其獨特的 FD-SOI 技術優勢,在功耗和抗軟錯誤率方面有很大優勢。如圖 1 所示,在基本的設計實現中,Certus-NX 晶片的功耗比英特爾和賽靈思的產品低 3-4 倍。萊迪思的晶片只出現 19 次軟錯誤故障(FIT),穩定性是其餘兩款產品的 160 倍。從 quad-SPI 記憶體啟動時,Certus-NX 的配置速度也比競品快 10 倍。其餘兩款產品均不提供 I/O 引腳瞬時啟動功能,而在 Certus-NX 上的回應時間僅為 3 ms。萊迪思還提 供 sensAI 解決方案集合,讓客戶能夠使用 Caffe 或 TensorFlow 工具開發神經網路。我們期待萊迪思今後可以在 Certus-NX 系列元件上提供這些功能。sensAI 還包括 RTL overlay, 可使用整數或二進位計算對 FPGA 程式設計,進行神經網路推理。

結論

Certus-NX 的諸多優勢可直接改善終端產品。其 6x6 mm 的小尺寸封裝可用於更小的電路板設計或節省空間便於添加新的系統功能。類似的 FPGA 競品封裝尺寸為 10x10 mm 到13x13 mm,門數相對較少的型號也是如此。儘管 Certus-NX 尺寸很小,但能提供更高的I/O 密度,為電路板設計人員提供了極大的靈活性。該晶片採用獨特的 FD-SOI 技術,比CMOS 製程功耗更低,實現了功耗和尺寸和全面優化。

對於通信和其他應用,Certus-NX 提供了硬邏輯實現 PCIe Gen2 和千兆乙太網介面,簡化了這些常用標準的實現。該元件靈活的 I/O 引腳速率高達 1.5 Gbps,能比競品 FPGA 更快地處理通信。

為了提高聯網設備的安全性,該系列 FPGA 還擁有加密模組,加速批量加密AES 和橢圓曲線(ECDSA)驗證。該模組還可以驗證外部配置記憶體,從而實現安全啟動。除 Certus-NX 外,沒有任何一款邏輯單元少於 100K 個 FPGA 擁有 ECDSA 模組。Certus-NX 初始化速度也比競品元件快 10 倍,大大減少了終端使用者等待其設備啟動的時間。

全新 FPGA 擁有一個 A/D 轉換器,可以搭配 IoT 設計中的模擬感測器。結合 PWM 模式下的可程式設計輸出,該ADC很適合用於電機控制。此外,Certus-NX 可以用作加速器,通過萊迪思sensAI 平台或邏輯單元上的特定演算法來實現神經網路。在這些設計中,FPGA可以通過高速PCIe介面直接連接到主機處理器,同時僅佔用少量引腳。FD-SOI 製程對軟錯誤具有天然的免疫力,因此 Certus-NX 是航空航太應用的理想選擇。然而,萊迪思的元件乘法器數量較少,不太適合 DSP 密集型應用。

Certus-NX 是基於萊迪思 Nexus 平台的第二款產品,它為廣泛的應用領域帶來了FD-SOI製程的優勢。這些通用FPGA可提供低功耗特性、小尺寸封裝和靈活的 I/O 以及 PCIe Gen2、千兆乙太網介面和高級加密功能。它們非常適用於各類網路邊緣應用,包括智慧家居、物聯網和消費電子網路。此外,它們還可以用於馬達控制和其他模擬應用,或者為AI和其他專用演算法提供低功耗高性能的加速服務。

(本文由萊迪思提供,作者Linley Gwennap為林利集團(The Linley Group)首席分析師)